|

|

PDF UPB8284 Data sheet ( Hoja de datos )

| Número de pieza | UPB8284 | |

| Descripción | CLOCK GENERATOR AND DRIVER | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPB8284 (archivo pdf) en la parte inferior de esta página. Total 7 Páginas | ||

|

No Preview Available !

NEe Microcomputers, Inc.

CLOCK GENERATOR AND DRIVER FOR

8086/8088 MICROPROCESSORS

N'EC

!J.PB8284

DESCR IPTION

The j.lPBB284 is a clock generator and driver for the B086 and 8088 microprocessors

This bipolar driver provides the microprocessor with a reset signal and also provides

properly synchronized READY timing. A TTL clock is also provided for peripheral

devices.

FEATU RES

• Generate System Clock for the 8086 and 8088

• Frequency Source can be a Crystal or a TTL Signal

• MOS Level Output for the Processor

• TTL Level Output for Peripheral Devices

• Power-Up Reset for the Processor

• READY Synchronization

• +5V Supply

• 18 Pin Package

PIN CONFIGURATION

CYSNC

PCLK

AENi'

RDY1

RDY2

AEiii2

CLK

GND

PIN NAMES

VCC

X1

X2

TNK

EFI

Fie

OSC

REs

RESET

X1. X2

TANK

FIC

EFI

CSYNC

RDY1}

RDY2

~}

AEN2

RES

RESET

OSC

CLK

PCLK

READY

Crystal Connections

For Overtone Crystal

Clock Source Select

External Clock Input

Clock Synchronization Input

Ready Signal from

Multibus™* Systems

Address Enable Qualifiers

for the two R DY Signals

Reset Input

Synchronized Reset Output

Oscillator Output

MOS Clock for the Processor

TTL Clock for Peripherals

Synchronized Ready Output

*TM - Multibus is a trademark of Intel Corporation.

II

673

1 page

,.,. PB8284

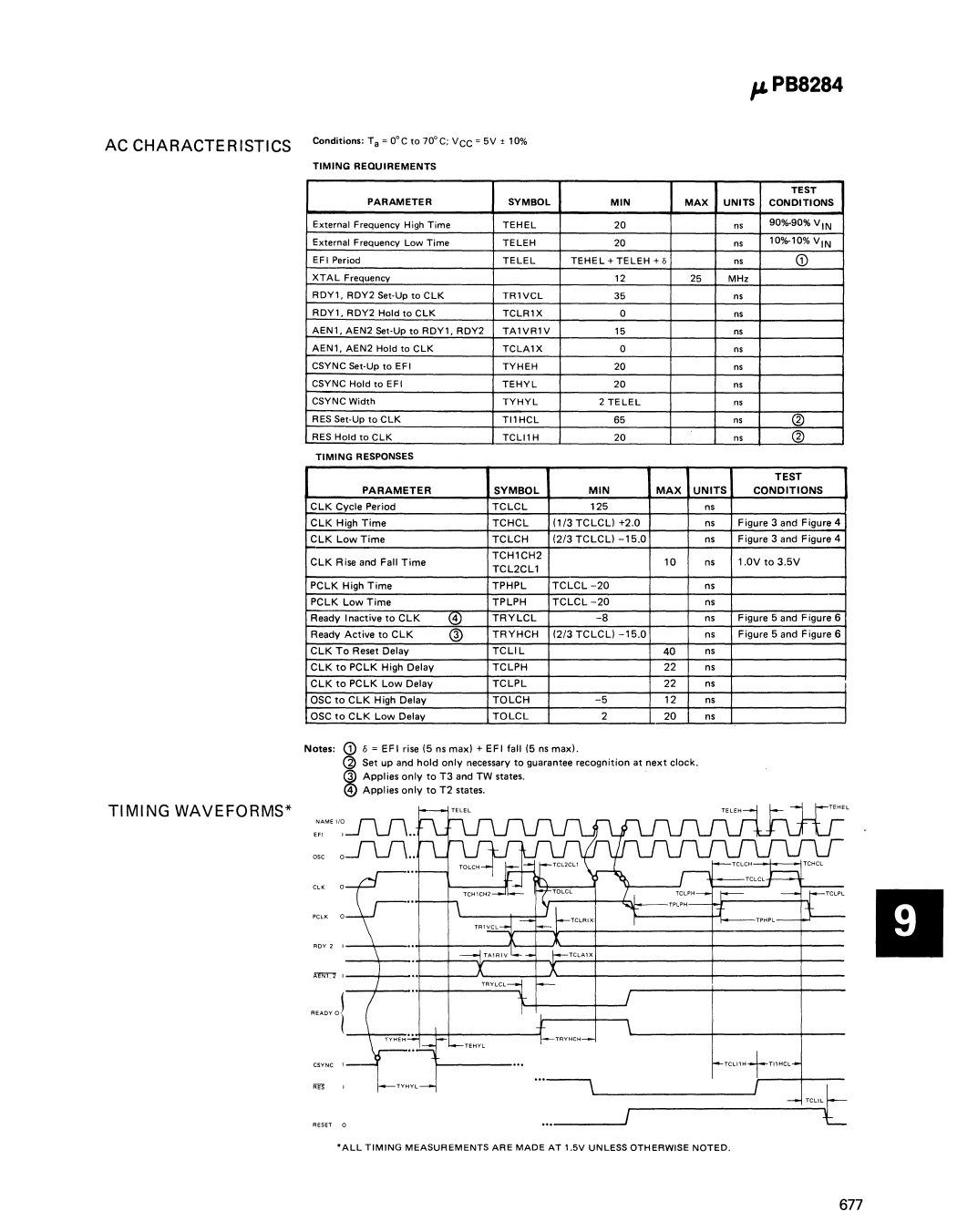

AC CHARACTERISTICS

TIMING REQUIREMENTS

PARAMETER

SYMBOL

MIN

TEST

MAX UNITS CONDITIONS

External Frequency High Time

External Frequency Low Time

EFI Period

XTAL Frequency

ROY1, RDY2 Set-Up to elK

ROY1, RDY2 Hold to elK

AEN1, AEN2 Set-Up to ROY1, RDY2

AEN1, AEN2 Hold to elK

CSYNC Set-Up to EFt

CSYNC Hold to EFt

CSYNCWidth

RES Set-Up to elK

RES Hold to elK

TIMING RESPONSES

TEHEL

TELEH

TELEL

TR1VCL

TCLR1X

TA1VR1V

TCLA1X

TYHEH

TEHYL

TVHYL

TllHCL

TCLI1H

20

20

TEHEL + TELEH + lj

12

35

0

15

0

20

20

2 TELEL

65

20

25

ns 90%-90% VIN

ns 10%-10% VIN

ns (j)

MHz

ns

ns

ns

ns

ns

ns

ns

ns @

ns @

PARAMETER

elK Cycle Period

elK High Time

elK Low Time

elK Rise and Fall Time

PCLK High Time

PCLK Low Time

Ready Inactive to elK

Ready Active to elK

elK To Reset Delay

CLK to PCLK High Delay

eLK to PClK low Delay

OSC to CLK High Delay

OSC to ClK low Delay

~

@

SYMBOL

TCLCL

TCHCL

TCLCH

TCH1CH2

TCL2CL1

TPHPL

TPLPH

TRYLCL

TRYHCH

TCLIL

TCLPH

TCLPL

TOLCH

TOLCL

MIN

125

11/3 TCLCL) +2.0

12/3 TCLCL) -15.0

TCLCL -20

TCLCL -20

-8

12/3 TCLCL) -15.0

-5

2

MAX

10

40

22

22

12

20

UNITS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

TEST

CONDITIDNS

Figure 3 and Figure 4

Figure 3 and Figure 4

1.0V to 3.5V

Figure 5 and Figure 6

Figure 5 and Figure 6

Notes:

CD 8 = EFI rise (5 ns max) + EFI fall (5 ns max).

~ Set up and hold only necessary to guarantee recognition at next clock.

3 Appl ies only to T3 and TW states.

4 Applies only to T2 states.

TIMING WAVEFORMS*

____~r-------------~"-mt=

+ALL TIMING MEASUREMENTS ARE MADE AT 1.5V UNLESS OTHERWISE NOTED.

677

5 Page | ||

| Páginas | Total 7 Páginas | |

| PDF Descargar | [ Datasheet UPB8284.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPB8282 | (UPB8282 / UPB8283) 8-BIT LATCHES | NEC |

| UPB8283 | (UPB8282 / UPB8283) 8-BIT LATCHES | NEC |

| UPB8284 | CLOCK GENERATOR AND DRIVER | NEC |

| UPB8284A | CLOCK GENERATOR AND DRIVER | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |