|

|

PDF UPD8021 Data sheet ( Hoja de datos )

| Número de pieza | UPD8021 | |

| Descripción | SINGLE CHIP 8-BIT MICROCOMPUTER | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD8021 (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

NEe Microcomputers, Inc.

NEe

ILPD8021

SINGLE CHIP 8·BIT

MICROCOMPUTER

DESCRIPTION

The NECIlPD8021 is a stand alone 8-bit parallel microcomputer incorporating the

following features usually found in external peripherals. The IlPD8021 contains:

1K x 8 bits of mask ROM program memory, 64 x 8 bits of RAM data memory, 21

I/O lines, an B-bit interval timer/event counter, and internal clock circuitry.

FEATURES

• 8-Bit Processor, ROM, RAM, I/O, Timer/Counter

• Single +5V Supply (+4.5V to +6.5V)

• NMOS Silicon Gate Technology

• 8.381ls Instruction Cycle Time

• All Instructions 1 or 2 Cycles

• Instructions are Subset of IlPD8048/8748/8035

• High Current Drive Capability - 2 I/O Pins

• Clock Generation Using Crystal or Single Inductor

• Zero-Cross Detection Capabil ity

• Expandable I/O Using 1l8243's

• Available in 28 Pin Plastic Package

PIN CONFIGURATION

Pn

P23

PROG

PO~

P01

P02

P03

P04

P07

ALE

T1

VSS

JlPD

8021

vee

P21

26 P20

25 P17

24 P16

23 P15

22 P14

21 P13

20 P12

19 Pll

18 PlO

17 RESET

16 XTAL2

15 XTAL 1

Rev/1

303

1 page

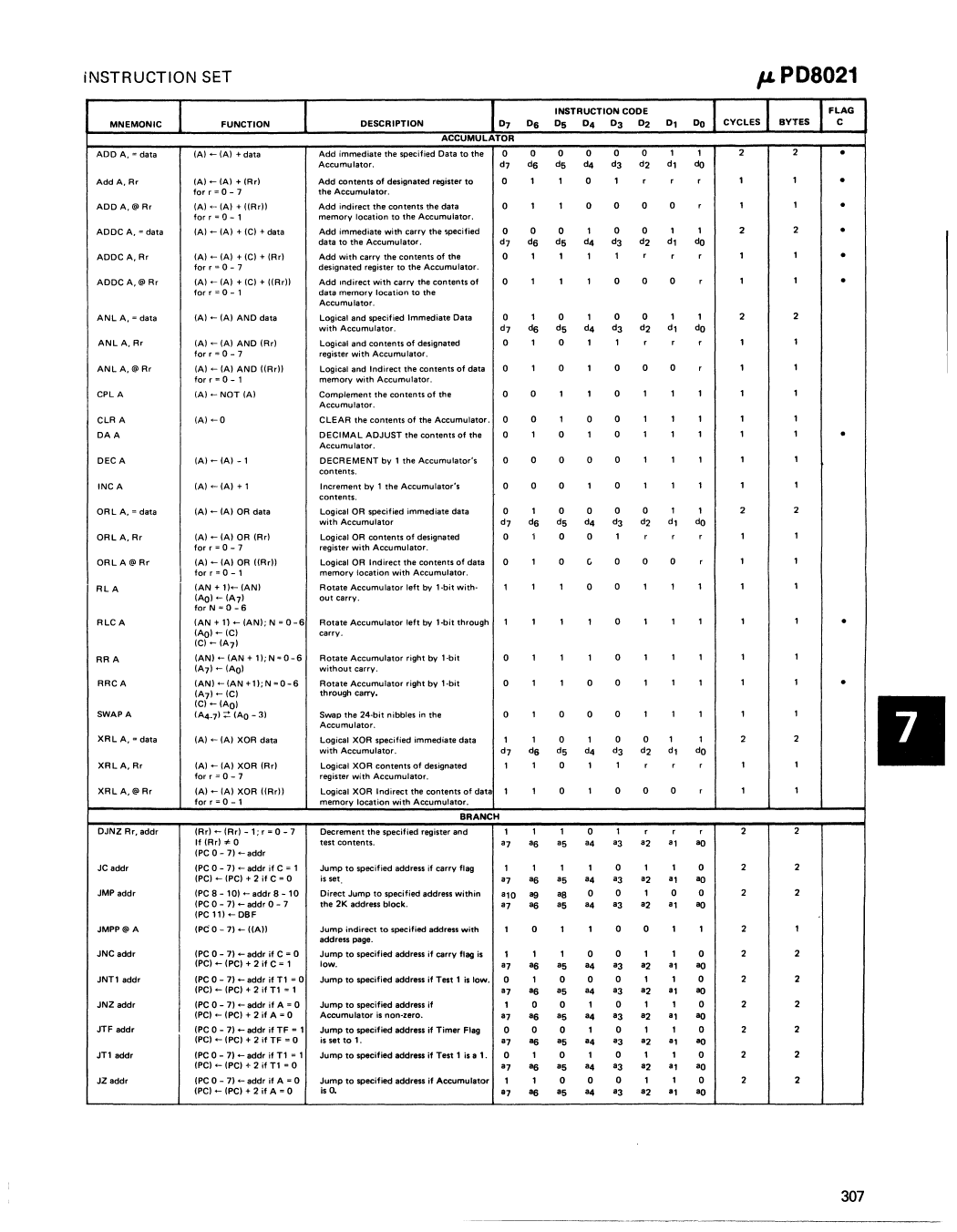

iNSTRUCTION SET

p.PD8021

MNEMONIC

ADD A, = data

Add A, Ar

ADDA,@Rr

ADDC A, = data

ADDe A, Ar

ADDC A,@Rr

ANL A, "" data

ANL A, Rr

ANL A,@Rr

CPL A

CLR A

DAA

DECA

INCA

ORL A, '" data

ORLA,Rr

ORL A@Rr

RL A

RLCA

RR A

RRCA

SWAP A

XRL A, '" data

XRL A, Rr

XRl A,@Rr

DJNZ Ar, addr

JC addr

JMP addr

JMPP@A

JNC addr

JNT1 addr

JNZ addr

JTF addr

JTl addr

JZ addr

FUNCTION

DESCRIPTION

INSTRUCTION CODE

07 06 D. DO 03 02 0, DO

(AI <- (A) + data

(AI +-- (AI + (Ar)

forr=0-7

(A) +-- (AI + ((Rd)

for r"'" 0 - 1

(AI +-- (A) + te) + data

(AI <-- (AI + (e) + (Ar)

forr;0-7

(AI +- (AI + (e) + ((Ar))

for r '" 0 - 1

, ,ACCUMULATOR

Add immediate the specified Data to the 0 0 0 0 0 0

Accumulator.

Add contents of designated register to

, , ,d7 d6 d. do d3 d2 d, dO

0 0 ,,,

the Accumulator.

Add indirect the contents the data

, , ,0 0 0 0 0

,memory location to the Accumulator.

Add immediate with carry the specified 0 0 0

00 11

data to the Accumulator.

Add with carry the contents of the

, , ,d7 d6 d. dO d3 d2 d, dO

01111

,designated register to the Accumulator.

Add Indirect with carry the contents of 0 1 1 1 0 0 0

data memory location to the

Accumulator.

(A) - (A) AND data

(A) <- (A) AND (Rr)

for r '" 0 - 7

(AI - (AI AND ((Rd)

for r '" 0 - 1

Logical and specified Immediate Data

0 1 0 10 0 11

with Accumulator.

Logical and contents of designated

, , , ,d7 d6 d. dO d3 d2 dl dO

0 0 11

register with Accumulator.

,Logical and Indirect the contents of data 0 1 0 1 0 0 0

memory with Accumulator.

(AI +- NOT (AI

Complement the contents of the

Accumulator.

0 0 1 10 111

IAI-O

CLEAR the contents of the Accumulator. 0 0 1 0 0 1 1 1

DECIMAL ADJUST the contents of the

0

1

0

1

0

1

1

1

Accumulator.

IAI-IAI-l

DECREMENT by 1 the Accumulator's

contents.

00000 111

(AI _(A) + 1

Increment by 1 the Accumulator's

contents.

00 0 10 1 11

(A) <- (A) OR data

(AI - (A) OR (Rr)

for r '" 0 - 7

IAI- IAI OR IIRdl

for r '" 0-1

Logical OR specified immediate data

0 10 0 0 0 11

with Accumulator

Logical OR contents of designated

, , ,d7 d6 d5 dO d3 d2 dl dO

0 100 1

register with Accumulator.

,Logical OR Indirect the contents of data 0 1 0 G 0 0 0

memory location with Accumulator.

(AN + 1)_ (AN)

IAOI- IA71

forN"'O-6

Rotate Accumulator left by '-bit with·

out carry.

11 100 111

(AN + 11- (AN); N '" 0-6 Rotate Accumulator left by '-bit through 1 1 1 1 0 1 1 1

IAOI-ICI

carry.

ICI- IA71

(AN) <- (AN + 1);N",O-6

IA71- IAOI

Rotate Accumulator right by l-bit

without carry.

0 1 1 10 1 11

(AN) - {AN +11; N =0-6

IA71-ICI

ICI-IAOI

(A4_7) ~ (AD - 3)

Rotate Accumulator right by l-bit

through carry.

Swap the 24·bit nibbles in the

Accu mu lator.

0 1 100 111

0 10 00 1 11

(AI - (A) XOR data

(A) +- (A) XOR (Rr)

forr=0-7

(A) <- (A) XOR ((Rd)

for r =0-1

Logical XOR specified immediate data

1 1 0 1 0 01 1

with Accumulator.

Logical XOR contents of designated

, , ,d7 d6 d5 dO d3 d2 d, dO

110 1 1

register with Accumulator.

,Logical XOR Indirect the contents of dats 1 1 0 1 0 0 0

memory location with Accumulator.

(Ad- (Rrl-l r-0-7

If (Ad *- 0

(PC 0 - 7) - addr

BRANCH

Decrement the specified register and

test contents.

'.1 1

'7 '6

10 1 ,,,

""'0 '3 '2 '1

(PC 0 - 7) +- addr if C = 1

(PC) <- (PC) + 2 if C = 0

(PCS-1O)+-addrS-l0

(PC 0 - 7) +-addr 0-7

(PC1l)-DBF

(PC 0 - 71 +- ((A))

Jump to specified address if carry flag

is set

Direct Jump to specified address within

the 2K address block.

Jump indirect to specified address witn

1 1 1 10 1 10

'7 '6

'0 '3 '2 '1 '0

. ''.. .'" '"0 '8 0 0 1 0 0

""'7 83 '2 '1

,1 0 1 1 0 0

1

address page.

, ,(PC 0 - 7) - addr if C = 0

(PC) +- (PCI + 2 if C = 1

Jump to specified address if carry flag is

1

low.

'7 86

0 0 1 10

'0 '3 82 81 '0

'.(PCO-71 +-addr ifn '" 0 Jump to specified address if Test 1 is low. 0 1 0 0 0 1 1 0

.. .(PC) - (PC) + 2 if T1 = 1

'7 '3 '2 '1

'. '"(PC 0 - 7) +- addr if A '" 0

.(PC) +- (PC) + 2 if A =0

Jump to specified address if

ACC1Jmulator is non-zero.

10

'7 '6

0

10 11

'3 '2 '1

0

. '. ""(PC 0 - 7) -addr ifTF = 1 Jump to specified address if Timer Flag 0 0

(PC) +- (PC) + 2 if TF = a

is set to 1.

'7

0 1 0 1 10

'0 83 82 '1 '0

'.(PC 0 - 7) +- addr if T1 = 1 Jump to specified address if Test 1 is a 1. 0 1 0 1 0 1 1 0

..(PC) +- (PC) + 2 if T1 '" 0

'7

80 '3 '2

'0

.. '. "(PCa - 7) -addr if A = 0

Jump to specified address if Accumulator 1

1

0

0

0

1

10

'. .(PC) +- (PC) + 2 if A = 0

ISO.

'7 "3 '2 81 '0

CYCLES

2

,

,

2

1

,

2

1

1

1

,

1

,

,

2

1

1

,

1

1

,

1

2

1

1

2

2

2

2

2

2

2

2

2

2

BYTES

2

,

,

2

1

,

2

1

1

1

1

1

1

1

2

1

1

1

1

1

1

1

2

1

1

2

2

2

,

2

2

2

2

2

2

FLAG

C

·

·····

·

·

·

II

307

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet UPD8021.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD8021 | SINGLE CHIP 8-BIT MICROCOMPUTER | NEC |

| UPD8022 | SINGLE CHIP 8-BIT MICROCOMPUTER | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |