|

|

PDF KSZ8775CLX Data sheet ( Hoja de datos )

| Número de pieza | KSZ8775CLX | |

| Descripción | Integrated 5-Port 10/100 Managed Ethernet Switch | |

| Fabricantes | Microchip | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de KSZ8775CLX (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

KSZ8775CLX

Integrated 5–Port 10/100 Managed Ethernet

Switch with Port 4 RMII and Port 5 RGMII/MII/

RMII Interfaces

Features

• Management Capabilities

- The KSZ8775CLX includes all the functions

of a 10/100BASE-T/TX switch system, which

combines a switch engine, frame buffer

management, address look-up table, queue

management, MIB counters, media access

controllers (MAC), and PHY transceivers

- Non-blocking store-and-forward switch fabric

assures fast packet delivery by utilizing a

1024-entry forwarding table

- Port mirroring/monitoring/sniffing: ingress

and/or egress traffic to any port

- MIB counters for fully compliant statistics

gathering - 36 counters per port

- Hardware support for port-based flush and

freeze command in MIB counter.

- Multiple loopback of remote, PHY, and MAC

modes support for the diagnostics

- Rapid spanning tree support (RSTP) for

topology management and ring/linear

recovery

• Robust PHY Ports

- Four integrated IEEE 802.3/802.3u-compliant

Ethernet transceivers supporting 10Base-T

and 100BASE-TX

- 802.1az EEE supported

- On-chip termination resistors and internal

biasing for differential pairs to reduce power

- HP Auto MDI/MDI-X™ crossover support

eliminates the need to differentiate between

straight or crossover cables in applications

• MAC and GMAC Ports

- Four internal media access control (MAC1 to

MAC4) units and one internal Gigabit media

access control (GMAC5) unit

- RGMII, MII, or RMII interfaces support for the

Port 5 GMAC5 with uplink and RMII interface

for Port 4 MAC4

- 2 kb jumbo packet support

- Tail tagging mode (one byte added before

FCS) support on Port 5 to inform the

processor which ingress port receives the

packet and its priority

- Supports reduced media independent inter-

face (RMII) with 50 MHz reference clock out-

put

- Supports media independent interface (MII)

in either PHY mode or MAC mode on Port 5

- LinkMD® cable diagnostic capabilities for

determining cable opens, shorts, and length

• Advanced Switch Capabilities

- Non-blocking store-and-forward switch fabric

assures fast packet delivery by utilizing a

1024-entry forwarding table

- 64kb frame buffer RAM

- IEEE 802.1q VLAN support for up to 128

active VLAN groups (full-range 4096 of VLAN

IDs)

- IEEE 802.1p/q tag insertion or removal on a

per port basis (egress)

- VLAN ID tag/untag options on per port basis

- Fully compliant with IEEE 802.3/802.3u stan-

dards

- IEEE 802.3x full-duplex with force mode

option and half-duplex back-pressure colli-

sion flow control

- IEEE 802.1w rapid spanning tree protocol

support

- IGMP v1/v2/v3 snooping for multicast packet

filtering

- QoS/CoS packets prioritization support:

802.1p, DiffServ-based and re-mapping of

802.1p priority field per port basis on four

priority levels

- IPv4/IPv6 QoS support

- IPv6 multicast listener discovery (MLD)

snooping

- Programmable rate limiting at the ingress and

egress ports on a per port basis

- Jitter-free per-packet-based rate limiting

support

- Tail tagging mode (one byte added before

FCS) support on Port 5 to inform the proces-

sor which ingress port receives the packet

and its priority

- Broadcast storm protection with percentage

control (global and per port basis)

DS00002129C-page 1

2015 Microchip Technology Inc.

1 page

KSZ8775CLX

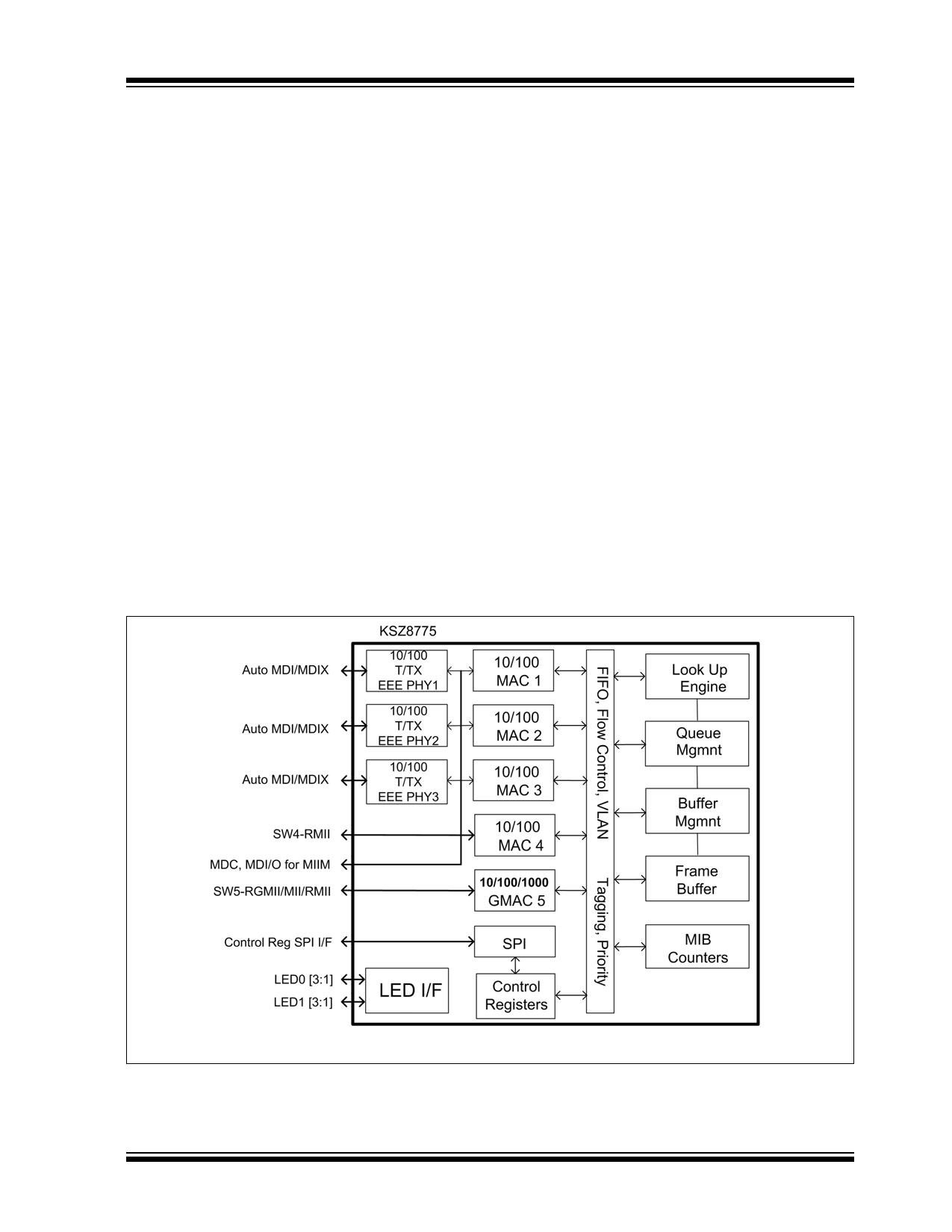

1.0 INTRODUCTION

1.1 General Description

The KSZ8775CLX is a highly integrated, Layer 2-managed, five-port switch with numerous features designed to reduce

system cost. It is intended for cost-sensitive applications requiring three 10/100 Mbps copper ports, one RMII on Port

4, and one 10/100/1000Mbps Gigabit uplink port on Port 5. The KSZ8775CLX incorporates a small package outline, the

lowest power consumption with internal biasing, and on-chip termination. Its extensive set of features include enhanced

power management, programmable rate limiting and priority ratio, tagged and port-based VLAN, port-based security

and ACL rule-based packet filtering technology, QoS priority with four queues, management interfaces, enhanced MIB

counters, high-performance memory bandwidth, and a shared memory-based switch fabric with non-blocking support.

The KSZ8775CLX provides support for multiple CPU data interfaces to effectively address both current and emerging

fast Ethernet and Gigabit Ethernet applications where the Port 5 GMAC can be configured to any of the RGMII, MII, and

RMII modes.

The KSZ8775CLX product is built upon industry-leading analog and digital technology, with features designed to offload

host processing and streamline the overall design.

• Three integrated 10/100BASE-T/TX MAC/PHYs

• One integrated 10/100BASE-T/TX MAC with RMII interface

• One integrated 10/100/1000Base-T/TX GMAC with selectable RGMII, MII, and RMII interfaces

• Small 80-pin LQFP package

A robust assortment of power management features including Energy Efficient Ethernet (EEE), power management

event (PME), and Wake-on-LAN (WoL) have been designed in to satisfy energy efficient environments.

All registers in the MAC/PHY units can be managed through the SPI interface. MIIM PHY registers can be accessed

through the MDC/MDIO interface.

FIGURE 1-1:

BLOCK DIAGRAM

2015 Microchip Technology Inc.

DS00002129C-page 5

5 Page

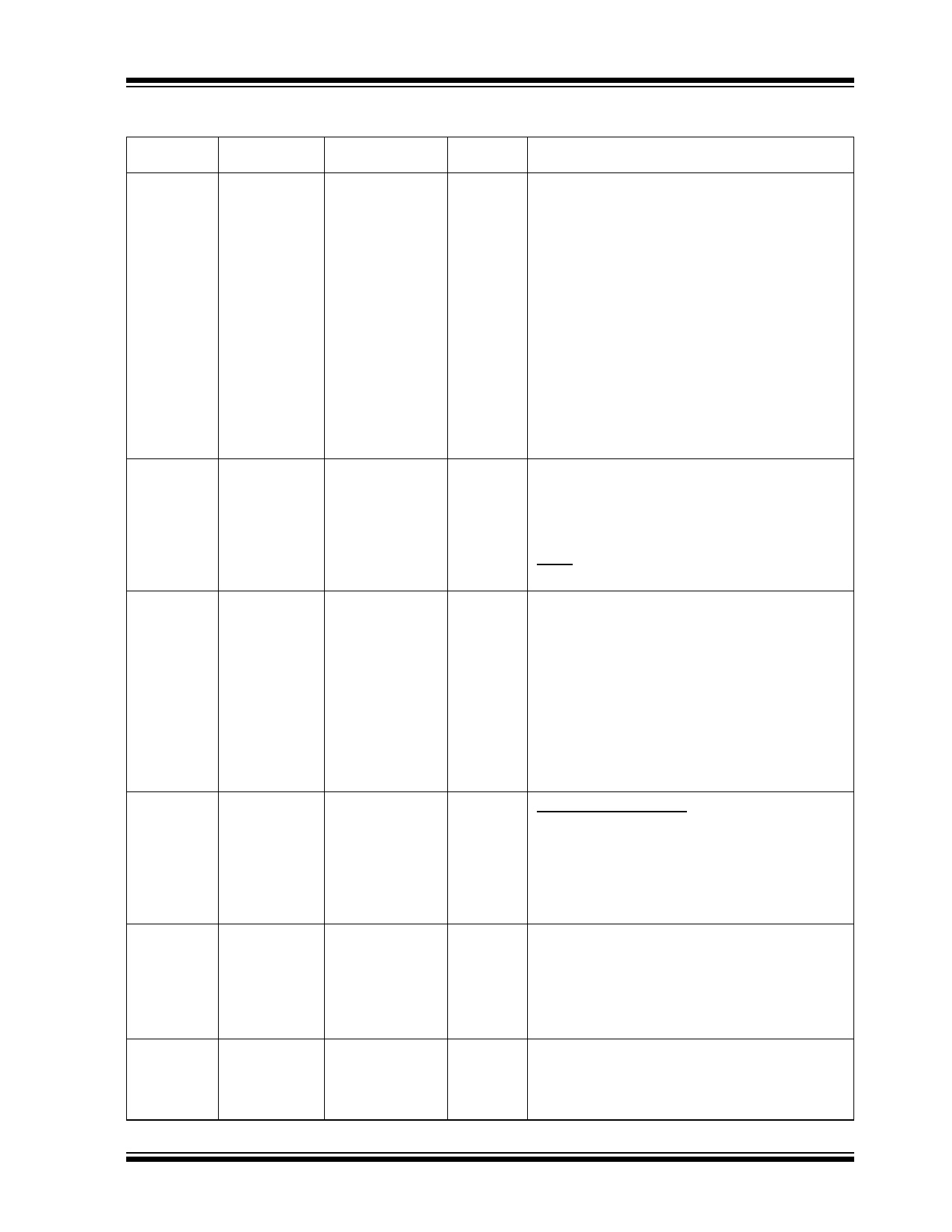

TABLE 2-1:

Num Pins

SIGNALS (CONTINUED)

Pin Name

Type

63 LED2_1

IPU/O

64 LED2_0

IPU/O

65 LED1_1

IPU/O

66 LED1_0

IPU/O

67 SPIQ

IPD/O

68 SCL_MDC

IPU

KSZ8775CLX

Port

2

2

1

1

All

All

Pin Description

Port 2 LED Indicator 1.

See global Register 11 bits [5:4] for details.

Strap option: Port 5 MII and RMII modes select

When Port 5 is MII mode:

PU = MAC mode.

PD = PHY mode.

When Port 5 is RMII mode:

PU = Clock mode in RMII, using 25 MHz OSC

clock and provide 50 MHz RMII clock from pin

RXC5.

PD = Normal mode in RMII, the TXC5/REFCLKI5

pin on the Port 5 RMII will receive an external

50 MHz clock

Note: Port 5 also can use either an internal or

external clock in RMII mode based on this strap

pin or the setting of the Register 86 (0x56) bit[7].

Port 2 LED Indicator 0.

See global Register 11 bits [5:4] for details.

Strap option: REFCLKO enable

PU = REFCLK_O (25 MHz) is enabled. (default)

PD = REFCLK_O is disabled

Note: It is better to disable this 25 MHz clock if

not providing an extra 25 MHz clock for system.

Port 1 LED Indicator 1.

See global Register 11 bits [5:4] for details.

Strap option: PLL clock source select

PU = Still use 25 MHz clock from XI/XO pins even

though it is in Port 5 RMII normal mode.

PD = Use external clock from TXC5 in Port 5 RMII

normal mode.

Note: If received clock in Port 5 RMII normal

mode has too much clock jitter, you can still select

the 25 MHz crystal/oscillator as the switch’s clock

source.

Port 1 LED Indicator 0.

See global Register 11 bits [5:4] for details.

Strap option: Speed select in Port 5 RGMII

PU = 1 Gbps in RGMII. (default)

PD = 10/100 Mbps in RGMII.

Note: Programmable through internal registers

also.

SPI Serial Data Output in SPI Slave Mode.

Strap option: Serial bus configuration

PD = SPI slave mode.

PU = MDC/MDIO mode.

Note: An external pull-up or pull-down resistor is

required.

Clock Input for SPI or MDC/MDIO Interface.

Input clock up to 50 MHz in SPI slave mode.

Input clock up to 25 MHz in MDC/MDIO for MIIM

access.

2015 Microchip Technology Inc.

DS00002129C-page 11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet KSZ8775CLX.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KSZ8775CLX | Integrated 5-Port 10/100 Managed Ethernet Switch | Microchip |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |