|

|

PDF SST49LF016C Data sheet ( Hoja de datos )

| Número de pieza | SST49LF016C | |

| Descripción | 16 Mbit LPC Serial Flash | |

| Fabricantes | Microchip | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SST49LF016C (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Obsolete Device

Please contact Microchip Sales for replacement information.

16 Mbit LPC Serial Flash

SST49LF016C

EOL Data Sheet

The SST49LF016C flash memory device is designed to interface with host con-

trollers (chipsets) that support a low pin-count (LPC) interface for system firmware

applications. Complying with LPC Interface Specification 1.1, SST49LF016C sup-

ports a Burst-Read data transfer of 15.6 MBytes per second at 33 MHz clock

speed and 31.2 MBytes per second at 66 MHz clock speed, up to 128 bytes in a

single operation

Features

• Operational Clock Frequency

– 33 MHz

– 66 MHz

• Organized as 2M x8

• Conforms to LPC Interface Specification v1.1

– Support Multi-Byte Firmware Memory Read/Write

Cycles

• Single 3.0-3.6V Read and Write Operations

• LPC Mode

– 5-signal LPC bus interface for both in-system and fac-

tory programming using programmer equipment

– Multi-Byte Read data transfer rate

15.6 MB/s @ 33 MHz PCI clock and

31.2 MB/s @ 66 MHz clock

- Firmware Memory Read cycle supporting

1, 2, 4, 16, and 128 Byte Read

- Firmware Memory Write cycle supporting

1, 2, and 4 Byte Write

– 33 MHz/66 MHz clock frequency operation

– WP#/AAI and TBL# pins provide hardware Write protect

for entire chip and/or top Boot Block

– Block Locking Registers for individual block Read-Lock,

Write-Lock, and Lock-Down protection

– 5 GPI pins for system design flexibility

– 4 ID pins for multi-chip selection

– Multi-Byte capability registers

(read-only registers)

– Status register for End-of-Write detection

– Program-/Erase-Suspend

Read or Write to other blocks during

Program-/Erase-Suspend

• Two-cycle Command Set

• Security ID Feature

– 256-bit Secure ID space

- 64-bit Unique Factory Pre-programmed Device Identi-

fier

- 192-bit User-Programmable OTP

• Superior Reliability

– Endurance: 100,000 Cycles (typical)

– Greater than 100 years Data Retention

• Low Power Consumption

– Active Read Current: 12 mA (typical)

– Standby Current: 10 µA (typical)

• Uniform 4 KByte sectors

– 35 Overlay Blocks: one 16-KByte Boot Block, two 8-

KByte Parameter Blocks, one 32-Kbyte Parameter

Block, thirty-one 64-KByte Main Blocks.

• Fast Sector-Erase/Program Operation

– Sector-Erase Time: 18 ms (typical)

– Block-Erase Time: 18 ms (typical)

– Program Time: 7 µs (typical)

• Auto Address Increment (AAI) for Rapid Factory

Programming (High Voltage Enabled)

– RY/BY# pin for End-of-Write detection

– Multi-Byte Program

– Chip Rewrite Time: 4 seconds (typical)

• Packages Available

– 32-lead PLCC

– 32-lead TSOP (8mm x 14mm)

– 40-lead TSOP (10mm x 20mm)

• All devices are RoHS compliant

© 2016

www.microchip.com

DS20005029B

02/16

1 page

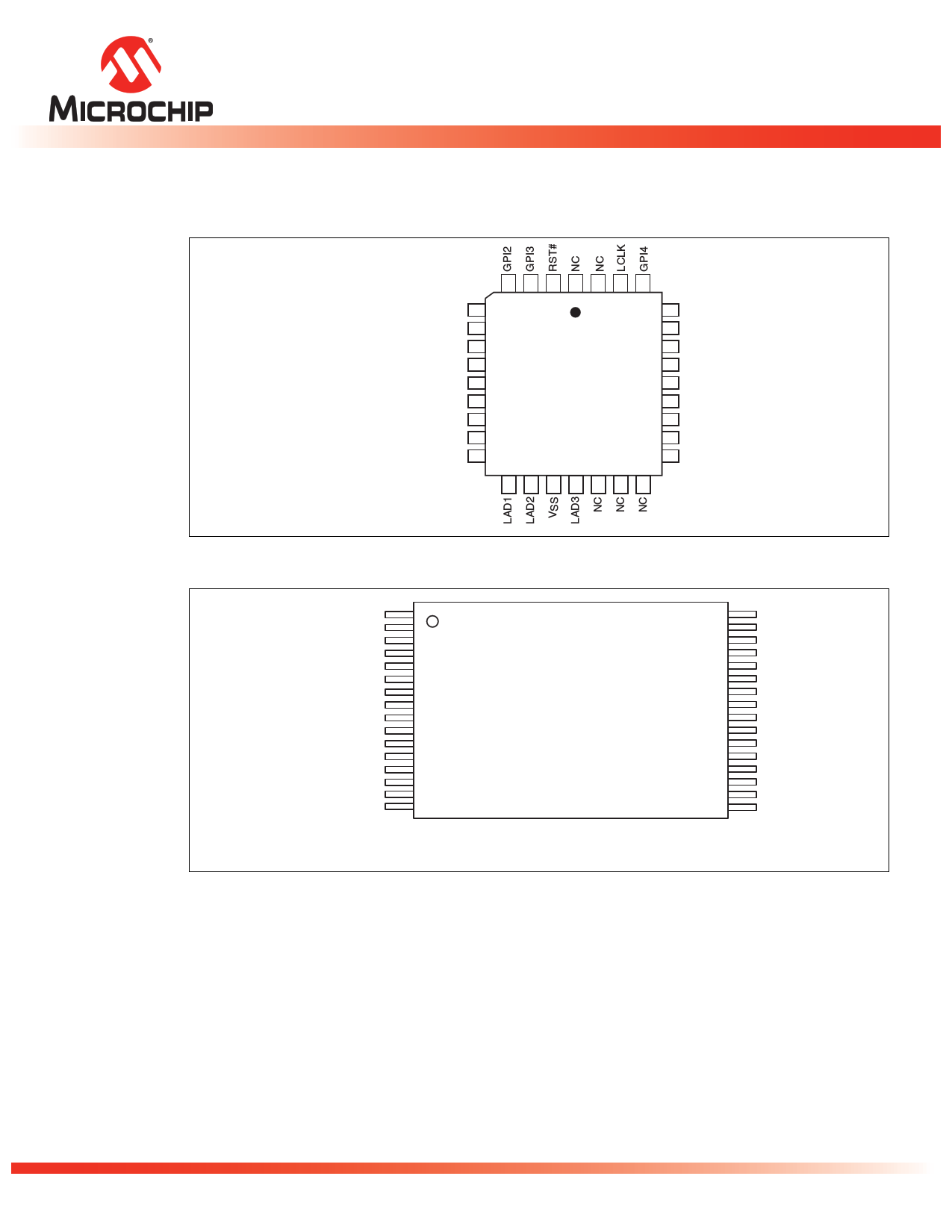

Pin Assignments

16 Mbit LPC Serial Flash

SST49LF016C

EOL Data Sheet

GPI1 (LD#)

GPI0 (RY/BY#)

WP#/AAI

TBL#

ID3

ID2

ID1

ID0

LAD0

4 3 2 1 32 31 30

5 29

6 28

7 27

8 32-lead PLCC 26

9 25

10

Top View

24

11 23

12 22

13 21

14 15 16 17 18 19 20

NC

NC

NC

NC

VDD

INIT#

LFRAME#

NC

NC

( ) Designates AAI Mode

Figure 3: Pin Assignments for 32-lead PLCC

1237 32-plcc P2.0

NC

NC

NC

NC

NC

GPI4

LCLK

NC

NC

RST#

GPI3

GPI2

GPI1 (LD#)

GPI0 (RY/BY#)

WP#/AAI

TBL#

( ) Designates AAI Mode

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32-lead TSOP

Top View

Figure 4: Pin Assignments for 32-lead TSOP

32 INIT#

31 LFRAME#

30 VDD

29 NC

28 NC

27 NC

26 NC

25 LAD3

24 VSS

23 LAD2

22 LAD1

21 LAD0

20 ID0

19 ID1

18 ID2

17 ID3

1237 32-tsop P1.0

© 2016

DS20005029B

02/16

5

5 Page

16 Mbit LPC Serial Flash

SST49LF016C

LPC Mode

EOL Data Sheet

Device Operation

The SST49LF016C supports Multi-Byte Firmware Memory Read and Write cycle types as defined in

Low Pin Count Interface Specification, Revision 1.1. Table 2 shows the size of transfer supported by

the SST49LF016C.

Table 2: Transfer Size Supported

Cycle Type

Firmware Memory Read

Firmware Memory Write

Size of Transfer

1, 2, 4, 16, 128 Bytes

1, 2, 4 Bytes

T2.1 20005029

The LPC mode uses a 5-signal communication interface: one control line, LFRAME#, which is driven

by the host to start or abort a bus cycle, a 4-bit data bus, LAD[3:0], used to communicate cycle type,

cycle direction, ID selection, address, data and sync fields. The device enters standby mode when

LFRAME# is taken high and no internal operation is in progress.

The host drives LFRAME# signal from low-to-high to capture the start field of a LPC cycle. On the

cycle in which LFRAME# goes inactive, the last latched value is taken as the START value. The START

value determines whether the SST49LF016C will respond to a Firmware Memory Read/Write cycle

type as defined in Table 3.

Table 3: Firmware Memory Cycles START Field Definition

START Value

1101

1110

Definition

Start of a Firmware Memory Read cycle

Start of a Firmware Memory Write cycle

T3.1 20005029

See following sections on details of Firmware Memory cycle types (Tables 4 and 5). Two-cycle Program

and Erase command sequences are used to initiate Firmware Memory Program and Erase operations. See

Table 8 for a listing of Program and Erase commands.

© 2016

DS20005029B

02/16

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SST49LF016C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SST49LF016C | 16 Mbit LPC Serial Flash | Microchip |

| SST49LF016C | 16 Mbit LPC Serial Flash | SST |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |