|

|

PDF LAN91C111 Data sheet ( Hoja de datos )

| Número de pieza | LAN91C111 | |

| Descripción | 10/100 Non-PCI Ethernet Single Chip MAC + PHY | |

| Fabricantes | Microchip | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LAN91C111 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

LAN91C111

10/100 Non-PCI Ethernet Single Chip MAC + PHY

Highlights

• Single Chip Ethernet Controller

• Dual Speed - 10/100 Mbps

• Fully Supports Full Duplex Switched Ethernet

• Supports Burst Data Transfer

• 8 Kbytes Internal Memory for Receive and Trans-

mit FIFO Buffers

• Enhanced Power Management Features

• Optional Configuration via Serial EEPROM Inter-

face

• Supports 8, 16 and 32 Bit CPU Accesses

• Internal 32 Bit Wide Data Path (Into Packet Buffer

Memory)

• Built-in Transparent Arbitration for Slave Sequen-

tial Access Architecture

• Flat MMU Architecture with Symmetric Transmit

and Receive Structures and Queues

• 3.3V Operation with 5V Tolerant IO Buffers (See

Pin List Description for Additional Details)

• Single 25 MHz Reference Clock for Both PHY and

MAC

• External 25Mhz-output pin for an external PHY

supporting PHYs physical media.

• Low Power CMOS Design

• Supports Multiple Embedded Processor Host

Interfaces

- ARM

- SH

- Power PC

- Coldfire

- 680X0, 683XX

- MIPS R3000

• 3.3V MII (Media Independent Interface) MAC-

PHY Interface Running at Nibble Rate

• MII Management Serial Interface

• 128-Pin QFP RoHS compliant package

• 128-Pin TQFP 1.0 mm height RoHS compliant

package

• Commercial Temperature Range from 0C to

70C (LAN91C111)

• Industrial Temperature Range from -40C to 85C

(LAN91C111i)

Network Interface

• Fully Integrated IEEE 802.3/802.3u-100Base-TX/

10Base-T Physical Layer

• Auto-Negotiation: 10/100, Full / Half Duplex

• On Chip Wave Shaping - No External Filters

Required

• Adaptive Equalizer

• Baseline Wander Correction

• LED Outputs (User selectable – Up to 2 LED func-

tions at one time)

- Link

- Activity

- Full Duplex

- 10/100

- Transmit

- Receive

2011-2016 Microchip Technology Inc.

DS00002276A-page 1

1 page

LAN91C111

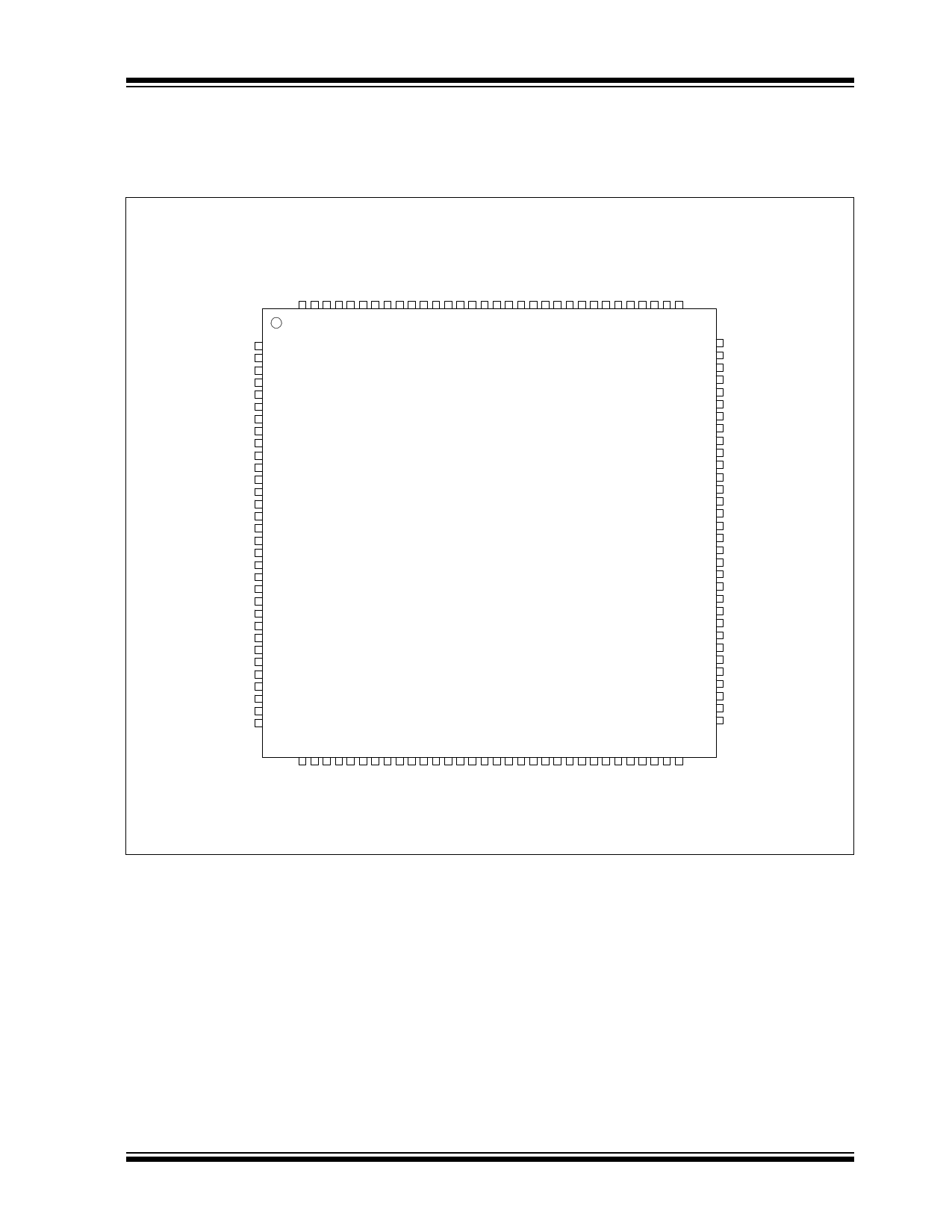

2.0 PIN CONFIGURATIONS

FIGURE 2-1:

PIN CONFIGURATION - LAN91C111-FEAST 128-PIN TQFP

VDD

nCSOUT

IOS0

IOS1

IOS2

ENEEP

EEDO

EEDI

EESK

EECS

AVDD

RBIAS

AGND

TPO+

TPO-

AVDD

TPI+

TPI-

AGND

nLNK

LBK

nLEDA

nLEDB

GND

MDI

MDO

MCLK

nCNTRL

INTR0

RESET

nRD

nWR

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

LAN91C111-

FEASTTM

128 PIN TQFP

96 nBE2

95 nBE1

94 nBE0

93 GND

92 A15

91 A14

90 A13

89 A12

88 A11

87 A10

86 A9

85 A8

84 A7

83 A6

82 A5

81 A4

80 A3

79 A2

78 A1

77 VDD

76 D8

75 D9

74 D10

73 D11

72 GND

71 D12

70 D13

69 D14

68 D15

67 GND

66 D16

65 D17

2011-2016 Microchip Technology Inc.

DS00002276A-page 5

5 Page

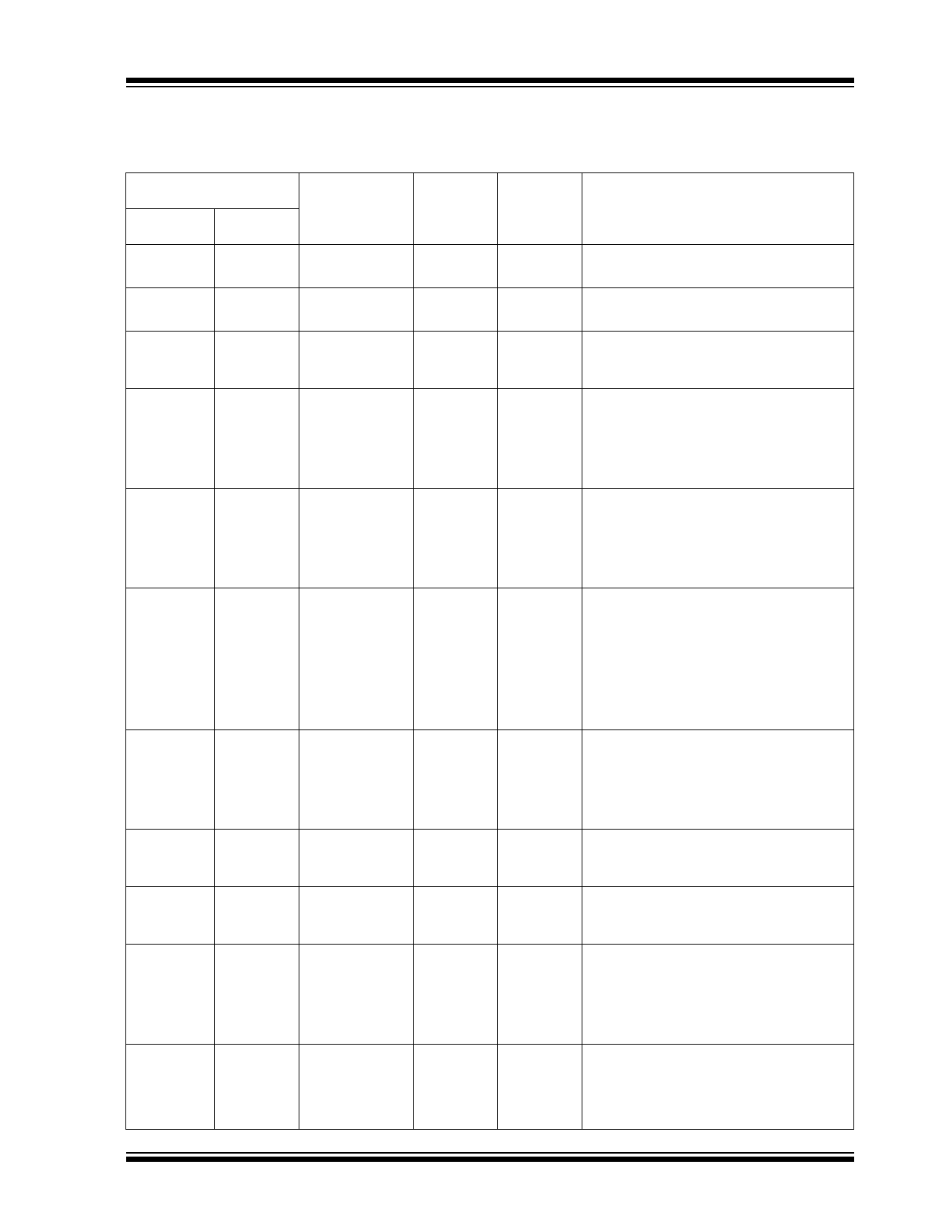

5.0 DESCRIPTION OF PIN FUNCTIONS

LAN91C111

Pin No.

TQFP

81-92

QFP

83-94

Name

Address

Symbol

Buffer

Type

A4-A15

I**

78-80

80-82

Address

A1-A3

I**

41

43

Address Enable AEN

I**

94-97

96-99

nByte Enable

nBE0-

nBE3

I**

107-104,

102-99, 76-

73, 71-68,

66-63, 61-

58, 56-53,

51-48

109-106,

104-101,

78-75, 73-

70, 68-65,

63-60, 58-

55, 53-50

Data Bus

30 32 Reset

D0-D31 I/O24**

RESET

IS**

37

39

nAddress

nADS

IS**

Strobe

35 37 nCycle nCYCLE I**

36 38 Write/

W/nR

IS**

nRead

40 42 nVL Bus Access nVLBUS I with

pullup**

42

44

Local Bus Clock LCLK

I**

Description

Input. Decoded by LAN91C111 to

determine access to its registers.

Input. Used by LAN91C111 for internal

register selection.

Input. Used as an address qualifier.

Address decoding is only enabled when

AEN is low.

Input. Used during LAN91C111 register

accesses to determine the width of the

access and the register(s) being

accessed. nBE0-nBE3 are ignored when

nDATACS is low (burst accesses)

because 32 bit transfers are assumed.

Bidirectional. 32 bit data bus used to

access the LAN91C111’s internal

registers. Data bus has weak internal

pullups. Supports direct connection to the

system bus without external buffering. For

16 bit systems, only D0-D15 are used.

Input. When this pin is asserted high, the

controller performs an internal system

(MAC & PHY) reset. It programs all the

registers to their default value, the

controller will read the EEPROM device

through the EEPROM interface (Note 5-1).

This input is not considered active unless

it is active for at least 100ns to filter

narrow glitches.

Input. For systems that require address

latching, the rising edge of nADS

indicates the latching moment for A1-A15

and AEN. All LAN91C111 internal

functions of A1-A15, AEN are latched

except for nLDEV decoding.

Input. This active low signal is used to

control LAN91C111 EISA burst mode

synchronous bus cycles.

Input. Defines the direction of

synchronous cycles. Write cycles when

high, read cycles when low.

Input. When low, the LAN91C111

synchronous bus interface is configured

for VL Bus accesses. Otherwise, the

LAN91C111 is configured for EISA DMA

burst accesses. Does not affect the

asynchronous bus interface.

Input. Used to interface synchronous

buses. Maximum frequency is 50 MHz.

Limited to 8.33 MHz for EISA DMA burst

mode. This pin should be tied high if it is

in asynchronous mode.

2011-2016 Microchip Technology Inc.

DS00002276A-page 11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet LAN91C111.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LAN91C110 | FEAST FAST ETHERNET CONTROLLER | SMSC Corporation |

| LAN91C111 | 10/100 Non-PCI Ethernet Single Chip MAC + PHY | Microchip |

| LAN91C111 | 10/100 Non-PCI Ethernet Single Chip MAC + PHY | SMSC Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |