|

|

PDF K4B8G1646B Data sheet ( Hoja de datos )

| Número de pieza | K4B8G1646B | |

| Descripción | DDP 8Gb B-die DDR3 SDRAM | |

| Fabricantes | Samsung | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de K4B8G1646B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Rev. 1.0, Feb. 2013

K4B8G1646B

DDP 8Gb B-die DDR3 SDRAM

96FBGA with Lead-Free & Halogen-Free Industrial

(RoHS compliant)

datasheet

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND

SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed

herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung

Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property

right is granted by one party to the other party under this document, by implication, estoppel or other-

wise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or

similar applications where product failure could result in loss of life or personal or physical harm, or any

military or defense application, or any governmental procurement to which special terms or provisions

may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

2013 Samsung Electronics Co., Ltd. All rights reserved.

-1-

1 page

K4B8G1646B

Rev. 1.0

datasheet Industrial DDP DDR3 SDRAM

1. Ordering Information

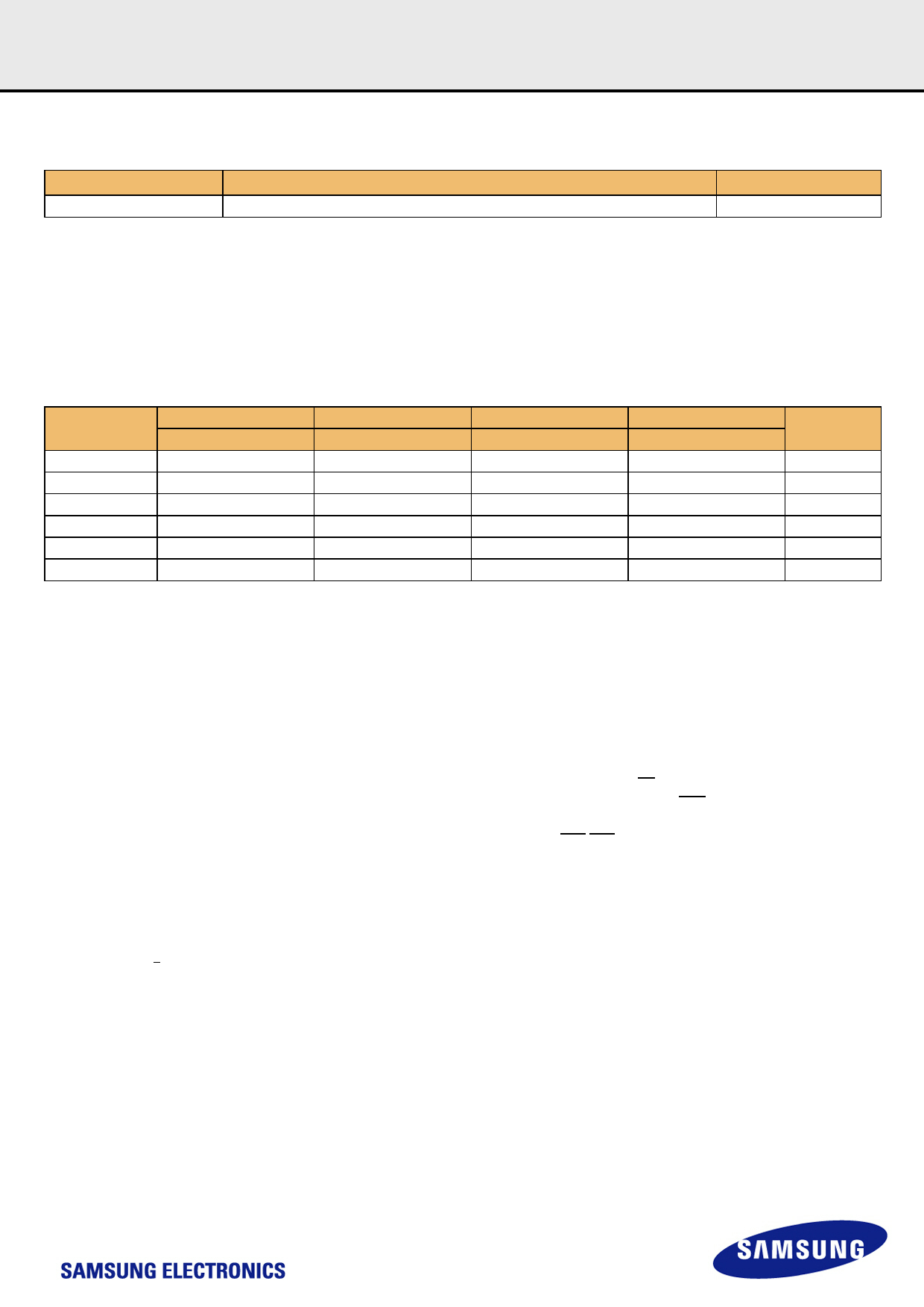

[ Table 1 ] Samsung DDP 8Gb DDR3 B-die ordering information table

Organization

DDR3-1600 (11-11-11)3

512Mx16

NOTE :

1. Speed bin is in order of CL-tRCD-tRP.

2.13th digit stands for below.

"I" : Industrial temp/Normal power

3. Backward compatible to DDR3-1333(9-9-9), DDR-1066(7-7-7)

K4B8G1646B-MIK0

Package

96 FBGA

2. Key Features

[ Table 2 ] DDP 8Gb DDR3 B-die Speed bins

Speed

DDR3-800

6-6-6

tCK(min)

2.5

CAS Latency

6

tRCD(min)

15

tRP(min)

15

tRAS(min)

37.5

tRC(min)

52.5

DDR3-1066

7-7-7

1.875

7

13.125

13.125

37.5

50.625

DDR3-1333

9-9-9

1.5

9

13.5

13.5

36

49.5

DDR3-1600

11-11-11

1.25

11

13.75

13.75

35

48.75

Unit

ns

nCK

ns

ns

ns

ns

• JEDEC standard 1.5V ± 0.075V Power Supply

• VDDQ = 1.5V ± 0.075V

• 400 MHz fCK for 800Mb/sec/pin, 533MHz fCK for 1066Mb/sec/pin,

667MHz fCK for 1333Mb/sec/pin, 800MHz fCK for 1600Mb/sec/pin

• 8 Banks

• Programmable CAS Latency(posted CAS): 6,7,8,9,10,11

• Programmable Additive Latency: 0, CL-2 or CL-1 clock

• Programmable CAS Write Latency (CWL) = 5 (DDR3-800), 6

(DDR3-1066), 7 (DDR3-1333) and 8 (DDR3-1600)

• 8-bit pre-fetch

• Burst Length: 8 (Interleave without any limit, sequential with starting

address “000” only), 4 with tCCD = 4 which does not allow seamless

read or write [either On the fly using A12 or MRS]

• Bi-directional Differential Data-Strobe

• Internal(self) calibration : Internal self calibration through ZQ pin

(RZQ : 240 ohm ± 1%)

• On Die Termination using ODT pin

• Average Refresh Period 7.8us at lower than TCASE 85C, 3.9us at

85C < TCASE < 95 C

• Support Industrial Temp ( -4095C )

- tREFI 7.8us at -40 °C ≤ TCASE ≤ 85°C

- tREFI 3.9us at 85 °C < TCASE ≤ 95°C

• Asynchronous Reset

• Package : 96 balls FBGA - x16

• All of Lead-Free products are compliant for RoHS

• All of products are Halogen-free

The DDP 8Gb DDR3 SDRAM B-die is organized as a 64Mbit x 16 I/Os x

8banks device. This synchronous device achieves high speed double-data-

rate transfer rates of up to 1600Mb/sec/pin (DDR3-1600) for general appli-

cations.

The chip is designed to comply with the following key DDR3 SDRAM fea-

tures such as posted CAS, Programmable CWL, Internal (Self) Calibration,

On Die Termination using ODT pin and Asynchronous Reset .

All of the control and address inputs are synchronized with a pair of exter-

nally supplied differential clocks. Inputs are latched at the crosspoint of dif-

ferential clocks (CK rising and CK falling). All I/Os are synchronized with a

pair of bidirectional strobes (DQS and DQS) in a source synchronous fash-

ion. The address bus is used to convey row, column, and bank address

information in a RAS/CAS multiplexing style. The DDR3 device operates

with a single 1.5V ± 0.075V power supply and 1.5V ± 0.075V VDDQ.

The DDP 8Gb DDR3 B-die device is available in 96ball FBGAs(x16).

NOTE :

1. This data sheet is an abstract of full DDR3 specification and does not cover the common features which are described in “DDR3 SDRAM Device Operation & Timing Dia-

gram”.

2. The functionality described and the timing specifications included in this data sheet are for the DLL Enabled mode of operation.

-5-

5 Page

K4B8G1646B

Rev. 1.0

datasheet Industrial DDP DDR3 SDRAM

6. Absolute Maximum Ratings

6.1 Absolute Maximum DC Ratings

[ Table 4 ] Absolute Maximum DC Ratings

Symbol

Parameter

Rating

Units

NOTE

VDD

VDDQ

VIN, VOUT

TSTG

Voltage on VDD pin relative to Vss

Voltage on VDDQ pin relative to Vss

Voltage on any pin relative to Vss

Storage Temperature

-0.4 V ~ 1.975 V

-0.4 V ~ 1.975 V

-0.4 V ~ 1.975 V

-55 to +100

V 1,3

V 1,3

V1

C 1, 2

NOTE :

1. Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the

device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions

for extended periods may affect reliability.

2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

3. VDD and VDDQ must be within 300mV of each other at all times; and VREF must be not greater than 0.6 x VDDQ, When VDD and VDDQ are less than 500mV; VREF may be

equal to or less than 300mV.

6.2 DRAM Component Operating Temperature Range

[ Table 5 ] Temperature Range

Symbol

Parameter

rating

Unit NOTE

TOPER

Operating Temperature Range

Normal

Industrial

0 to 95

-40 to 95

C 1, 2, 4

C 1, 3, 4

NOTE :

1. Operating Temperature TOPER is the case surface temperature on the center/top side of the DRAM. For measurement conditions, please refer to the JEDEC document

JESD51-2.

2. The Normal Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be main-

tained between 0-85C under all operating conditions

3. The Industrial Temperature Range specifies the temperatures where all DRAM specifications will be supported. During operation, the DRAM case temperature must be main-

tained between -40-85C under all operating conditions

4. Some applications require operation of the Extended Temperature Range between 85C and 95C case temperature. Full specifications are guaranteed in this range, but the

following additional conditions apply:

a) Refresh commands must be doubled in frequency, therefore reducing the refresh interval tREFI to 3.9us.

b) If Self-Refresh operation is required in the Extended Temperature Range, then it is mandatory to use the Manual Self-Refresh mode with Extended Temperature Range

capability (MR2 A6 = 0b and MR2 A7 = 1b).

7. AC & DC Operating Conditions

7.1 Recommended DC operating Conditions (SSTL_1.5)

[ Table 6 ] Recommended DC Operating Conditions

Symbol

Parameter

Min.

VDD Supply Voltage

1.425

VDDQ

Supply Voltage for Output

1.425

NOTE :

1. Under all conditions VDDQ must be less than or equal to VDD.

2. VDDQ tracks with VDD. AC parameters are measured with VDD and VDDQ tied together.

Rating

Typ.

1.5

1.5

Max.

1.575

1.575

Units

V

V

NOTE

1,2

1,2

- 11 -

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet K4B8G1646B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4B8G1646B | DDP 8Gb B-die DDR3 SDRAM | Samsung |

| K4B8G1646Q | DDP 8Gb Q-die DDR3L SDRAM | Samsung |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |