|

|

PDF FDMS3604S Data sheet ( Hoja de datos )

| Número de pieza | FDMS3604S | |

| Descripción | MOSFET ( Transistor ) | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de FDMS3604S (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

FDMS3604S

PowerTrench® Power Stage

January 2015

Asymmetric Dual N-Channel MOSFET

Features

Q1: N-Channel

Max rDS(on) = 8 mΩ at VGS = 10 V, ID = 13 A

Max rDS(on) = 11 mΩ at VGS = 4.5 V, ID = 11 A

Q2: N-Channel

Max rDS(on) = 2.8 mΩ at VGS = 10 V, ID = 23 A

Max rDS(on) = 3.5 mΩ at VGS = 4.5 V, ID = 21 A

Low inductance packaging shortens rise/fall times, resulting in

lower switching losses

MOSFET integration enables optimum layout for

lower circuit inductance and reduced switch node

ringing

RoHS Compliant

General Description

This device includes two specialized N-Channel MOSFETs in a

dual PQFN package. The switch node has been internally

connected to enable easy placement and routing of synchronous

buck converters. The control MOSFET (Q1) and synchronous

SyncFETTM (Q2) have been designed to provide optimal power

efficiency.

Applications

Computing

Communications

General Purpose Point of Load

Notebook VCORE

G1 D1 D1 D1

D1

PHASE

(S1/D2)

G2S2S2 S2

Top

Power 56

Bottom

MOSFET Maximum Ratings TA = 25 °C unless otherwise noted

Symbol

VDS

VDSt

VGS

ID

EAS

PD

TJ, TSTG

Parameter

Drain to Source Voltage

Drain to Source Transient Voltage ( tTransient < 100 ns)

Gate to Source Voltage

Drain Current -Continuous (Package limited)

-Continuous (Silicon limited)

-Continuous

-Pulsed

Single Pulse Avalanche Energy

Power Dissipation for Single Operation

Power Dissipation for Single Operation

Operating and Storage Junction Temperature Range

Thermal Characteristics

S2 5

S2 6

S2 7

G2 8

Q2 4 D1

PHASE

3 D1

2 D1

Q1 1 G1

(Note 3)

TC = 25 °C

TC = 25 °C

TA = 25 °C

TA = 25 °C

TA = 25 °C

Q1 Q2

30 30

33 33

±20 ±20

30 40

60

131a

130

231b

40

404

2.21a

1.01c

100

605

2.51b

1.01d

-55 to +150

Units

V

V

V

A

mJ

W

°C

RθJA

RθJA

RθJC

Thermal Resistance, Junction to Ambient

Thermal Resistance, Junction to Ambient

Thermal Resistance, Junction to Case

Package Marking and Ordering Information

571a

1251c

3.5

501b

1201d

2

°C/W

Device Marking

22CA

N7CC

Device

FDMS3604S

©2011 Fairchild Semiconductor Corporation

FDMS3604S Rev.C5

Package

Power 56

1

Reel Size

13 ”

Tape Width

12 mm

Quantity

3000 units

www.fairchildsemi.com

1 page

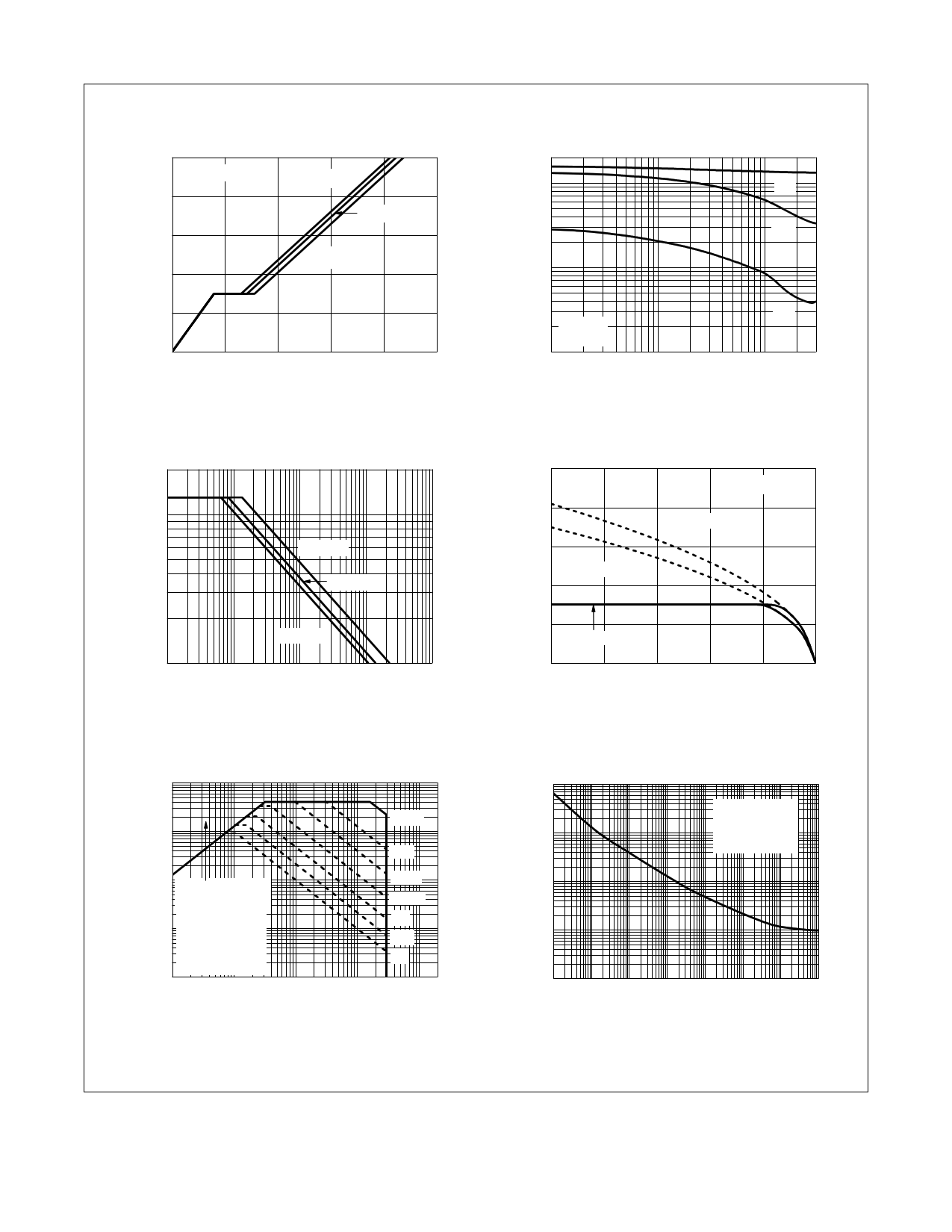

Typical Characteristics (Q1 N-Channel) TJ = 25 °C unless otherwise noted

10

ID = 13 A

8

6

4

VDD = 10 V

VDD = 15 V

VDD = 20 V

2000

1000

100

Ciss

Coss

2

0

0 5 10 15 20 25

Qg, GATE CHARGE (nC)

Figure 7. Gate Charge Characteristics

Crss

f = 1 MHz

VGS = 0 V

10

0.1 1 10

VDS, DRAIN TO SOURCE VOLTAGE (V)

30

Figure8. Capacitance vsDrain

to Source Voltage

20

10

TJ = 25 oC

TJ = 100 oC

1

0.01

TJ = 125 oC

0.1 1 10

tAV, TIME IN AVALANCHE (ms)

Figure9. UnclampedInductive

Switching Capability

100

100

100us

10

1 ms

1

THIS AREA IS

LIMITED BY rDS(on)

10 ms

100 ms

SINGLE PULSE

0.1 TJ = MAX RATED

RθJA = 125 oC/W

TA = 25 oC

0.01

0.01 0.1

1

1s

10s

DC

10 100 200

VDS, DRAIN to SOURCE VOLTAGE (V)

Figure 11. Forward Bias Safe

Operating Area

100

80

60

VGS = 4.5 V

40

RθJC = 3.5 oC/W

VGS = 10 V

20

Limited by Package

0

25 50 75 100 125

TC, CASE TEMPERATURE (oC)

150

Figure 10. Maximum Continuous Drain

Current vs Case Temperature

1000

100

10

SINGLE PULSE

RθJA = 125 oC/W

TA = 25 oC

1

0.1

10-4 10-3 10-2 10-1

1

10

t, PULSE WIDTH (sec)

100 1000

Figure 12. Single Pulse Maximum

Power Dissipation

©2011 Fairchild Semiconductor Corporation

FDMS3604S Rev.C5

5

www.fairchildsemi.com

5 Page

Application Information

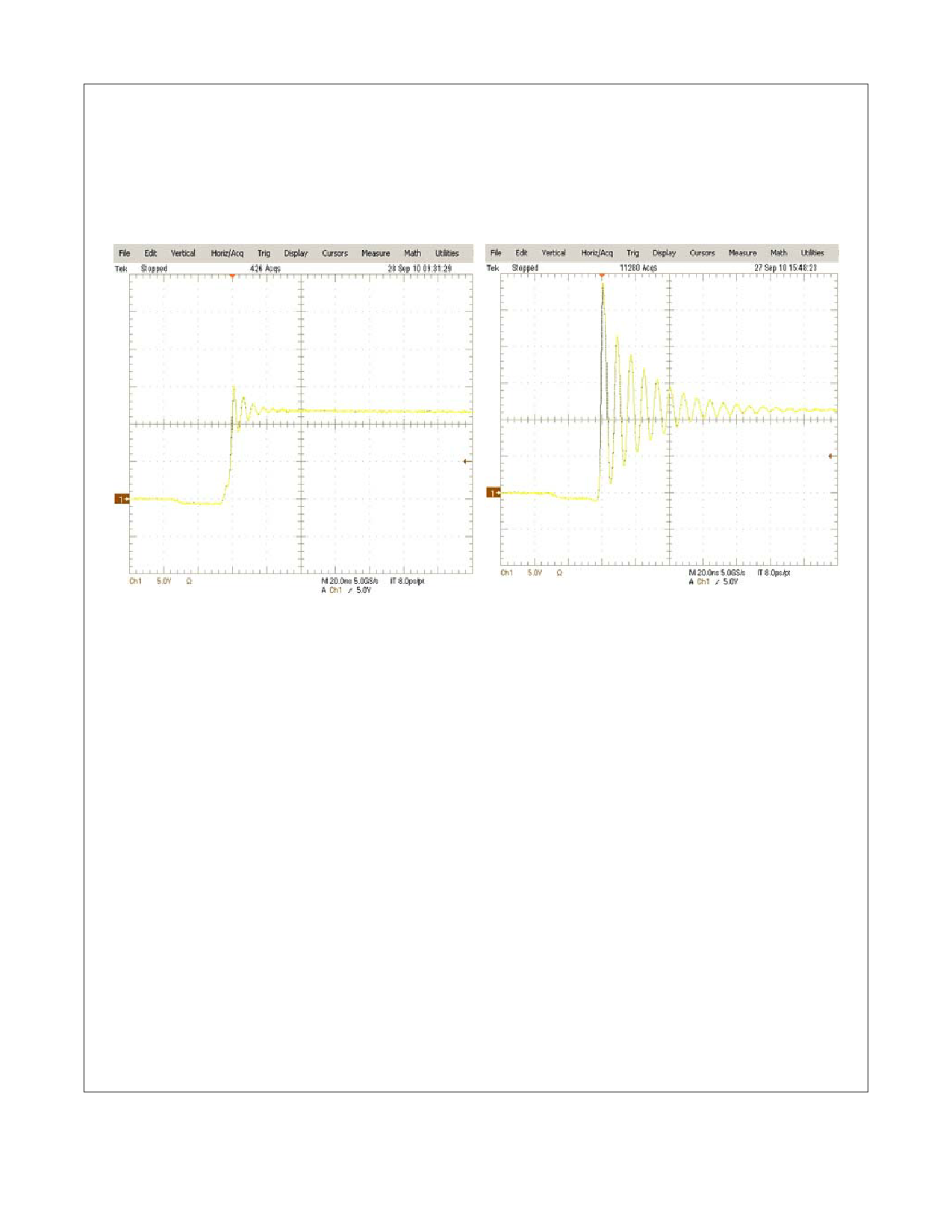

1. Switch Node Ringing Suppression

Fairchild’s Power Stage products incorporate a proprietary design* that minimizes the peak overshoot, ringing voltage on the switch

node (PHASE) without the need of any external snubbing components in a buck converter. As shown in the figure 29, the Power Stage

solution rings significantly less than competitor solutions under the same set of test conditions.

Power Stage Device

Competitors solution

Figure 29. Power Stage phase node rising edge, High Side Turn on

*Patent Pending

©2011 Fairchild Semiconductor Corporation

FDMS3604S Rev.C5

11

www.fairchildsemi.com

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet FDMS3604S.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| FDMS3604AS | MOSFET ( Transistor ) | Fairchild Semiconductor |

| FDMS3604S | MOSFET ( Transistor ) | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |