|

|

PDF DP7259 Data sheet ( Hoja de datos )

| Número de pieza | DP7259 | |

| Descripción | Quad Digital Potentiometer | |

| Fabricantes | COPAL ELECTRONICS | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de DP7259 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

Quad Digital Potentiometers

(DP) with 256 Taps and 2-wire Interface

DP7259

FEATURES

Four linear taper digital potentiometers

256 resistor taps per potentiometer

End to end resistance 50k or 100k

Potentiometer control and memory access via

2-wire interface (I2C like)

Low wiper resistance, typically 100

Nonvolatile memory storage for up to four

wiper settings for each potentiometer

Automatic recall of saved wiper settings at

power up

2.5 to 6.0 volt operation

Standby current less than 1µA

1,000,000 nonvolatile WRITE cycles

100 year nonvolatile memory data retention

24-lead SOIC and 24-lead TSSOP packages

Industrial temperature range

For Ordering Information details, see page 15.

DESCRIPTION

The DP7259 is four digital potentiometers

(DPs) integrated with control logic and 16 bytes

of NVRAM memory. Each DP consists of a series

of resistive elements connected between two

externally accessible end points. The tap points

between each resistive element are connected to the

wiper outputs with CMOS switches. A separate 8-bit

control register (WCR) independently controls the

wiper tap switches for each DP. Associated with

each wiper control register are four 8-bit non-volatile

memory data registers (DR) used for storing up to four

wiper settings. Writing to the wiper control register or

any of the non-volatile data registers is via a 2-wire

serial bus. On power-up, the contents of the first data

register (DR0) for each of the four potentiometers

is automatically loaded into its respective wiper

control registers.

The DP7259 can be used as a potentiometer or as a

two terminal, variable resistor. It is intended for circuit

level or system level adjustments in a wide variety of

applications. It is available in the -40ºC to 85ºC

industrial operating temperature ranges and offered in

a 24-lead SOIC and TSSOP package.

PIN CONFIGURATION

SOIC (W)

TSSOP (Y)

NC 1

A0 2

RW3

RH3

RL3

3

4

5

NC 6

VCC 7

RLO 8

RHO 9

RWO 10

A2 11

¯W¯P¯ 12

24 A3

23 SCL

22 RL2

21 RH2

20 RW2

19 NC

18 GND

17 RW1

16 RH1

15 RL1

14 A1

13 SDA

FUNCTIONAL DIAGRAM

SCL

SDA

WP

A0

A1

A2

A3

RH0

RH1

RH2

RH3

2-WIRE BUS

INTERFACE

WIPER CONTROL

REGISTERS

CONTROL LOGIC

NONVOLATILE

DATA

REGISTERS

RW0

RW1

RW2

RW3

RL0 RL1 RL2

RL3

© NIDEC COPAL ELECTRONICS CORP.

Characteristics subject to change without notice

1

Doc. No. MD-2000 Rev. H

1 page

Power Up Timing (1)(2)

Symbol

tPUR

tPUW

Parameter

Power-up to Read Operation

Power-up to Write Operation

DP Timing

Symbol Parameter

tWRPO Wiper Response Time After Power Supply Stable

tWRL Wiper Response Time After Instruction Issued

Write Cycle Limits (3)

Symbol Parameter

tWR Write Cycle Time

Reliability Characteristics

Symbol

NEND(4)

TDR(4)

VZAP(4)

ILTH(4)

Parameter

Endurance

Data Retention

ESD Susceptibility

Latch-Up

Reference Test Method

MIL-STD-883, Test Method 1033

MIL-STD-883, Test Method 1008

MIL-STD-883, Test Method 3015

JEDEC Standard 17

DP7259

Max

1

1

Units

ms

ms

Min Max Units

5 10 µs

5 10 µs

Max

5

Units

ms

Min

1,000,000

100

2000

100

Max

Units

Cycles/Byte

Years

V

mA

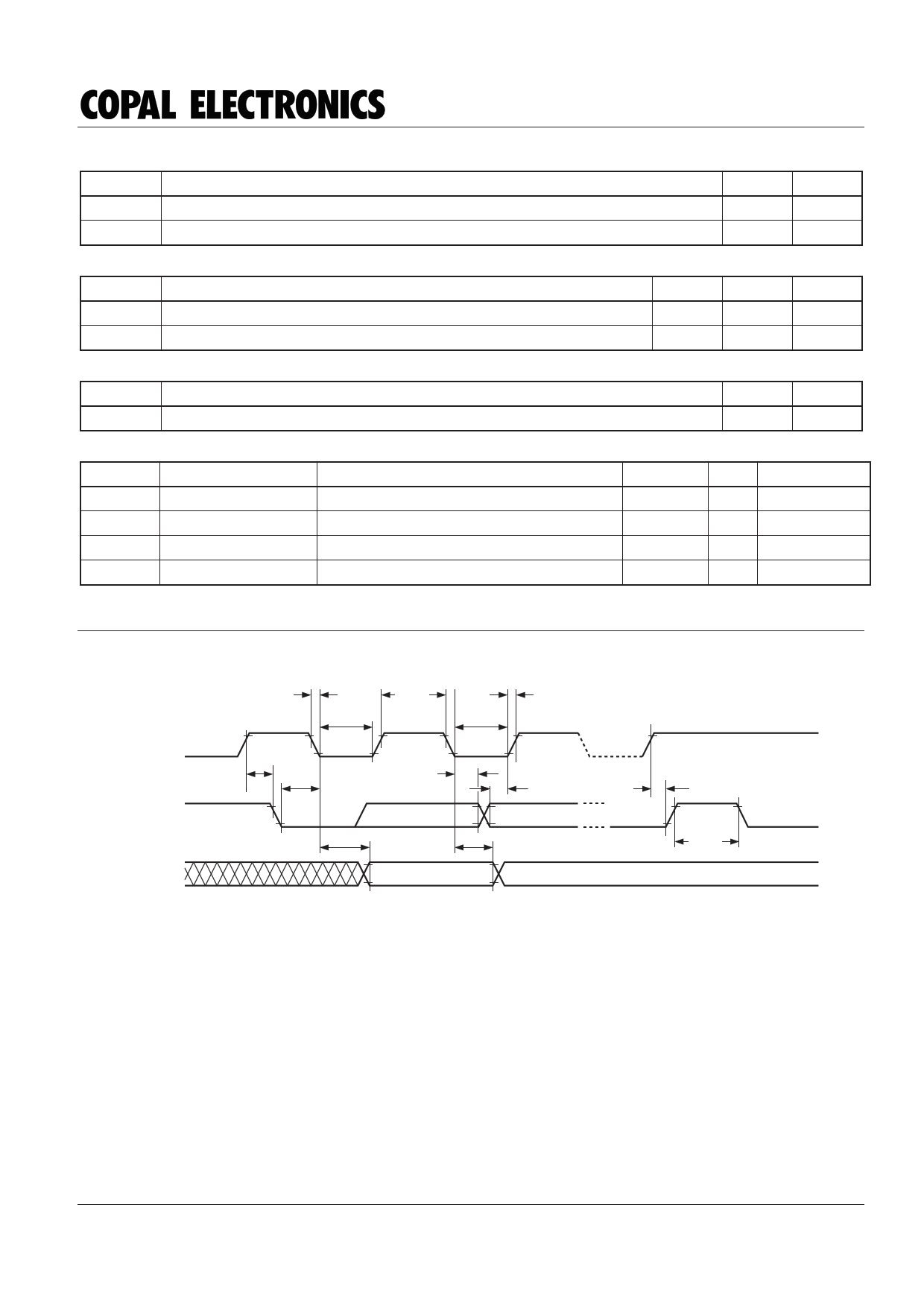

Figure 1. Bus Timing

tF tHIGH tR

tLOW

tLOW

SCL

tSU:STA

tHD:DAT

tHD:STA

tSU:DAT

SDA IN

SDA OUT

tAA tDH

tSU:STO

tBUF

Notes:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

(2) tPUR and tPUW are delays required from the time VCC is stable until the specified operation can be initiated.

(3) The write cycle is the time from a valid stop condition of a write sequence to the end of the internal program/erase cycle. During the write

cycle, the bus interface circuits are disabled, SDA is allowed to remain high, and the device does not respond to its slave address.

(4) This parameter is tested initially and after a design or process change that affects the parameter.

© NIDEC COPAL ELECTRONICS CORP.

Characteristics subject to change without notice

5

Doc. No. MD-2000 Rev. H

5 Page

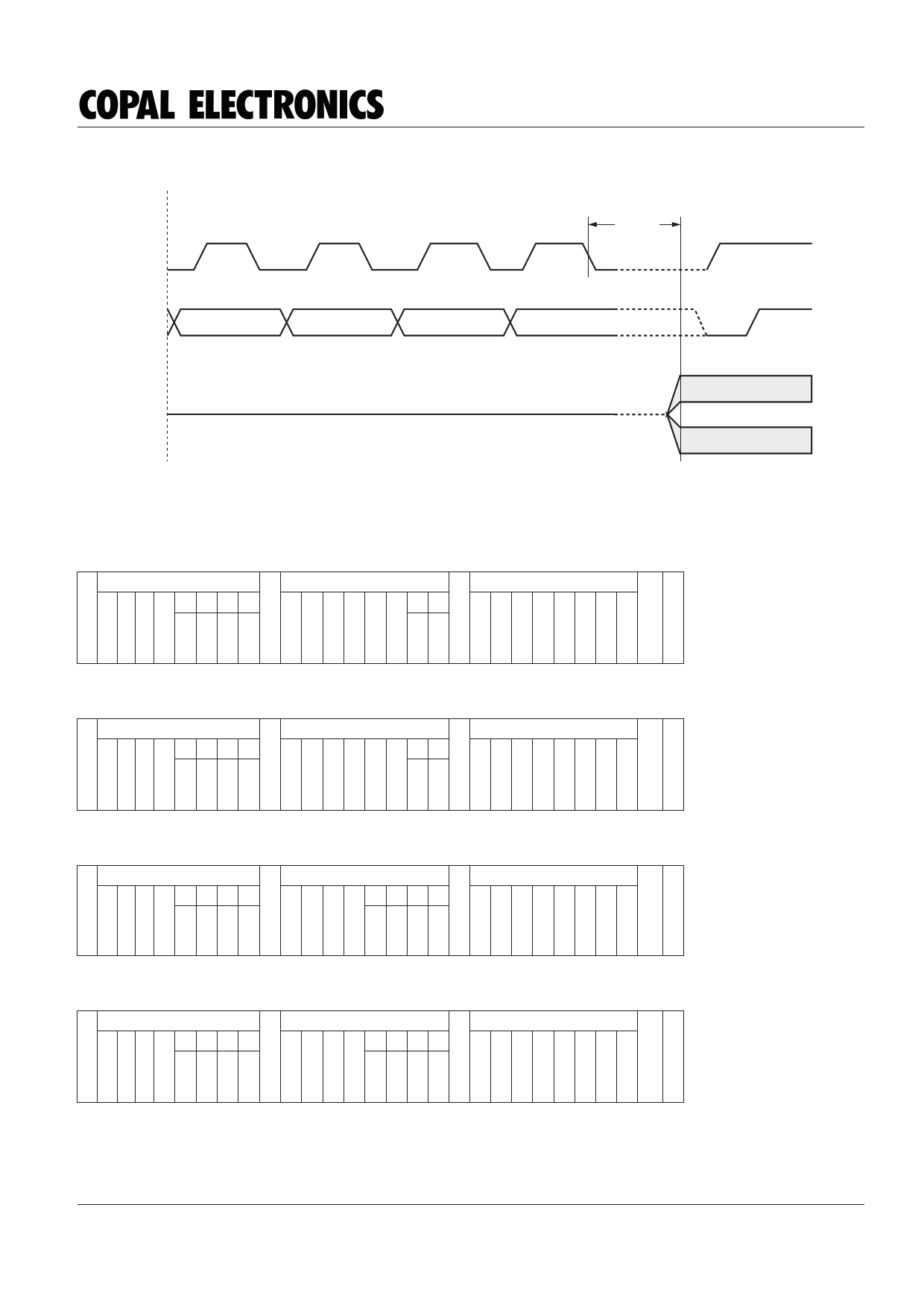

Figure 10. Increment/Decrement Timing Limits

INC/DEC

Command

Issued

SCL

SDA

RW Voltage Out

tWRL

INSTRUCTION FORMAT

Read Wiper Control Register (WCR)

S DEVICE ADDRESSES A INSTRUCTION A

DATA

AS

T0101 AAAAC1 0 0 1 0 0 PPC7 6 5 4 3 2 1 0 C T

A 3210K

R

10K

KO

P

T

Write Wiper Control Register (WCR)

S DEVICE ADDRESSES A INSTRUCTION A

DATA

AS

T0101 AAAAC1 0 1 0 0 0 PPC7 6 5 4 3 2 1 0 C T

A 3210K

R

10K

KO

P

T

Read Data Register (DR)

S DEVICE ADDRESSES A INSTRUCTION A

DATA

AS

T0101 AAAAC1 0 1 1RRPPC7 6 5 4 3 2 1 0 C T

A 3210K

R

1010K

KO

P

T

Write Data Register (DR)

S DEVICE ADDRESSES A INSTRUCTION A

DATA

AS

T0101 AAAAC1 1 0 0RRPPC7 6 5 4 3 2 1 0 C T

A 3210K

R

1010K

KO

P

T

DP7259

© NIDEC COPAL ELECTRONICS CORP.

Characteristics subject to change without notice

11

Doc. No. MD-2000 Rev. H

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet DP7259.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DP7251 | Quad Digital Potentiometer | COPAL ELECTRONICS |

| DP7259 | Quad Digital Potentiometer | COPAL ELECTRONICS |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |