|

|

PDF S29GL128N Data sheet ( Hoja de datos )

| Número de pieza | S29GL128N | |

| Descripción | 3.0V single power flash memory | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S29GL128N (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

S29GL512N

S29GL256N

S29GL128N

512, 256, 128 Mbit, 3 V, Page Flash

Featuring 110 nm MirrorBit

This product family has been retired and is not recommended for designs. For new and current designs, S29GL128S, S29GL256S,

and S29GL512T supersede the S29GL128N, S29GL256N, and S29GL512N respectively. These are the factory-recommended

migration paths. Please refer to the S29GL-S and S29GL-T Family data sheets for specifications and ordering information.

Distinctive Characteristics

Architectural Advantages

Single Power Supply Operation

– 3 volt read, erase, and program operations

Enhanced VersatileI/O Control

– All input levels (address, control, and DQ input levels) and outputs

are determined by voltage on VIO input. VIO range is 1.65 to VCC

Manufactured on 110 nm MirrorBit Process Technology

Secured Silicon Sector Region

– 128-word/256-byte sector for permanent, secure identification

through an 8-word/16-byte random Electronic Serial Number,

accessible through a command sequence

– May be programmed and locked at the factory or by the customer

Flexible Sector Architecture

– S29GL512N: Five hundred twelve 64 Kword (128 Kbyte) sectors

– S29GL256N: Two hundred fifty-six 64 Kword (128 Kbyte) sectors

– S29GL128N: One hundred twenty-eight 64 Kword (128 Kbyte)

sectors

Compatibility with JEDEC Standards

– Provides pinout and software compatibility for single-power supply

flash, and superior inadvertent write protection

100,000 Erase Cycles per sector typical

20-year Data Retention typical

Performance Characteristics

High Performance

– 90 ns access time (S29GL128N, S29GL256N)

– 100 ns (S29GL512N)

– 8-word/16-byte page read buffer

– 25 ns page read times

– 16-word/32-byte write buffer reduces overall programming time for

multiple-word updates

Low Power Consumption (typical values at 3.0 V, 5 MHz)

– 25 mA typical active read current;

– 50 mA typical erase/program current

– 1 µA typical standby mode current

Package Options

– 56-pin TSOP

– 64-ball Fortified BGA

Software & Hardware Features

Software Features

– Program Suspend and Resume: read other sectors before

programming operation is completed

– Erase Suspend and Resume: read/program other sectors before

an erase operation is completed

– Data# polling and toggle bits provide status

– Unlock Bypass Program command reduces overall multiple-word

programming time

– CFI (Common Flash Interface) compliant: allows host system to

identify and accommodate multiple flash devices

Hardware Features

– Advanced Sector Protection

– WP#/ACC input accelerates programming time (when high

voltage is applied) for greater throughput during system

production. Protects first or last sector regardless of sector

protection settings

– Hardware reset input (RESET#) resets device

– Ready/Busy# output (RY/BY#) detects program or erase cycle

completion

Product Availability Table

Density

512 Mb

256 Mb

128 Mb

Init. Access

110 ns

100 ns

110 ns

100 ns

90 ns

110 ns

100 ns

90 ns

VCC

Full

Full

Full

Full

Regulated

Full

Full

Regulated

Availability

Now

Now

Now

Now

Now

Now

Now

Now

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 002-01522 Rev. *B

• San Jose, CA 95134-1709 • 408-943-2600

Revised January 08, 2016

1 page

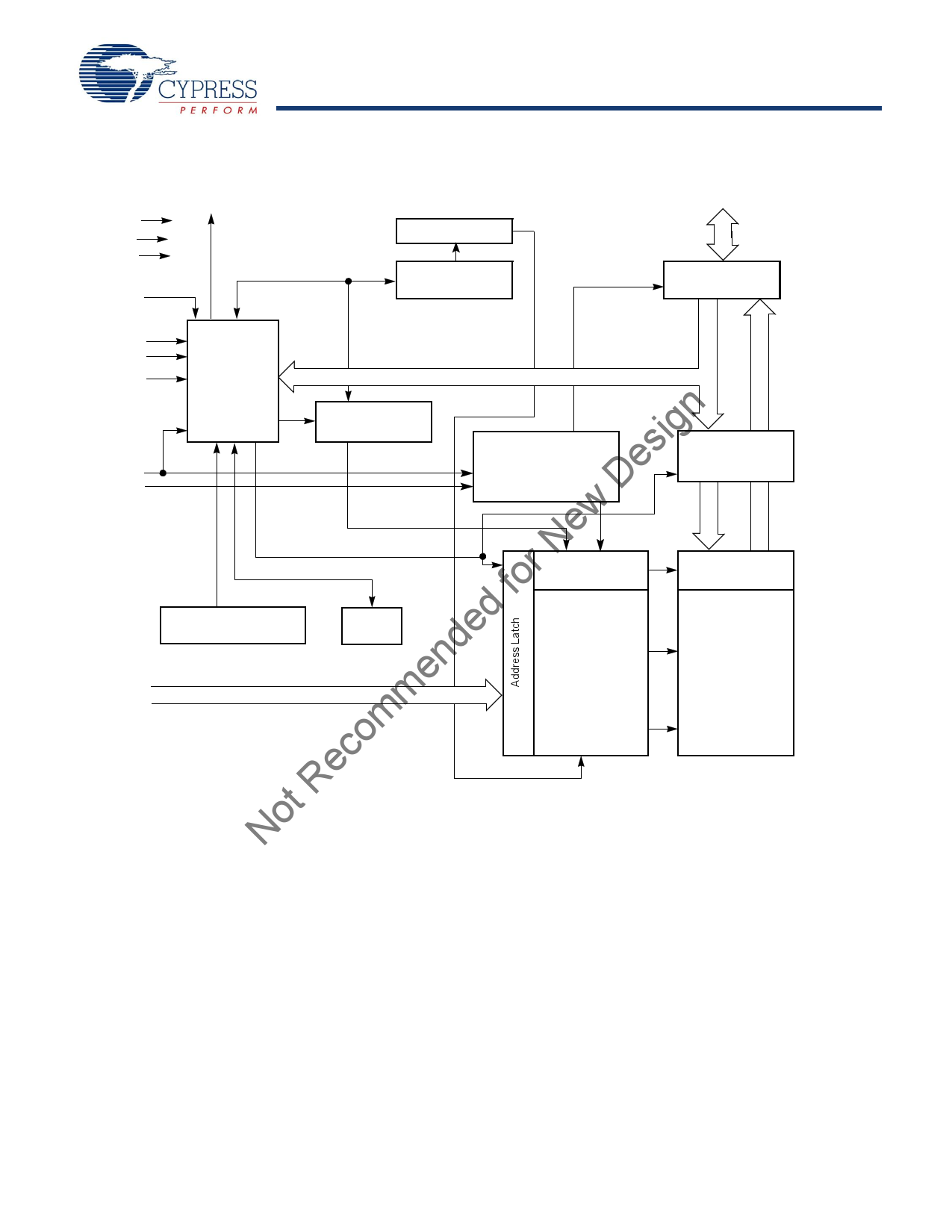

2. Block Diagram

VCC

VSS

VIO

RY/BY#

RESET#

WE#

WP#/ACC

BYTE#

State

Control

Command

Register

CE#

OE#

AMax**–A0

VCC Detector

Sector Switches

Erase Voltage

Generator

S29GL512N

S29GL256N

S29GL128N

DQ15–DQ0 (A-1)

Input/Output

Buffers

PGM Voltage

Generator

Chip Enable

Output Enable

Logic

STB

Data

Latch

Timer

STB

Y-Decoder

X-Decoder

Y-Gating

Cell Matrix

Note

** AMax GL512N = A24, AMax GL256N = A23, AMax GL128N = A22

Document Number: 002-01522 Rev. *B

Page 5 of 92

5 Page

S29GL512N

S29GL256N

S29GL128N

See Reading Array Data on page 43 for more information. Refer to the AC Read-Only Operations table for timing specifications and

to Figure 15.1 on page 68 for the timing diagram. Refer to the DC Characteristics table for the active current specification on reading

array data.

7.3.1 Page Mode Read

The device is capable of fast page mode read and is compatible with the page mode Mask ROM read operation. This mode provides

faster read access speed for random locations within a page. The page size of the device is 8 words/16 bytes. The appropriate page

is selected by the higher address bits A(max)–A3. Address bits A2–A0 in word mode (A2–A-1 in byte mode) determine the specific

word within a page. This is an asynchronous operation; the microprocessor supplies the specific word location.

The random or initial page access is equal to tACC or tCE and subsequent page read accesses (as long as the locations specified by

the microprocessor falls within that page) is equivalent to tPACC. When CE# is de-asserted and reasserted for a subsequent access,

the access time is tACC or tCE. Fast page mode accesses are obtained by keeping the “read-page addresses” constant and changing

the “intra-read page” addresses.

7.4 Writing Commands/Command Sequences

To write a command or command sequence (which includes programming data to the device and erasing sectors of memory), the

system must drive WE# and CE# to VIL, and OE# to VIH.

The device features an Unlock Bypass mode to facilitate faster programming. Once the device enters the Unlock Bypass mode,

only two write cycles are required to program a word or byte, instead of four. The “Word Program Command Sequence” section has

details on programming data to the device using both standard and Unlock Bypass command sequences.

An erase operation can erase one sector, multiple sectors, or the entire device. Table on page 13, Table on page 31, and Table

on page 34 indicate the address space that each sector occupies.

Refer to the DC Characteristics table for the active current specification for the write mode. The AC Characteristics section contains

timing specification tables and timing diagrams for write operations.

7.4.1 Write Buffer

Write Buffer Programming allows the system write to a maximum of 16 words/32 bytes in one programming operation. This results in

faster effective programming time than the standard programming algorithms. See Write Buffer on page 11 for more information.

7.4.2 Accelerated Program Operation

The device offers accelerated program operations through the ACC function. This is one of two functions provided by the WP#/ACC

pin. This function is primarily intended to allow faster manufacturing throughput at the factory.

If the system asserts VHH on this pin, the device automatically enters the aforementioned Unlock Bypass mode, temporarily

unprotects any protected sector groups, and uses the higher voltage on the pin to reduce the time required for program operations.

The system would use a two-cycle program command sequence as required by the Unlock Bypass mode. Removing VHH from the

WP#/ACC pin returns the device to normal operation. Note that the WP#/ACC pin must not be at VHH for operations other than

accelerated programming, or device damage may result. WP# has an internal pull-up; when unconnected, WP# is at VIH.

7.4.3 Autoselect Functions

If the system writes the autoselect command sequence, the device enters the autoselect mode. The system can then read

autoselect codes from the internal register (which is separate from the memory array) on DQ7–DQ0. Standard read cycle timings

apply in this mode. Refer to the Autoselect Mode on page 34 and Autoselect Command Sequence on page 44, for more information.

7.5 Standby Mode

When the system is not reading or writing to the device, it can place the device in the standby mode. In this mode, current

consumption is greatly reduced, and the outputs are placed in the high impedance state, independent of the OE# input.

The device enters the CMOS standby mode when the CE# and RESET# pins are both held at VIO ± 0.3 V. (Note that this is a more

restricted voltage range than VIH.) If CE# and RESET# are held at VIH, but not within VIO ± 0.3 V, the device is in the standby mode,

Document Number: 002-01522 Rev. *B

Page 11 of 92

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S29GL128N.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S29GL128M | MirrorBit Flash Family | ETC |

| S29GL128M | 3.0V single power Flash memory | SPANSION |

| S29GL128N | MirrorBit Flash Family | ETC |

| S29GL128N | 3.0V single power flash memory | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |