|

|

PDF NCP3134 Data sheet ( Hoja de datos )

| Número de pieza | NCP3134 | |

| Descripción | 4A Integrated Synchronous Buck Converter | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NCP3134 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

NCP3134

4 A Integrated Synchronous

Buck Converter

NCP3134 is a fully integrated synchronous buck converter for 3.3 V

and 5 V step−down applications. It can provide up to 4 A load current.

NCP3134 supports high efficiency, fast transient response and

provides power good indicator. The control scheme includes two

operation modes: FCCM and automatic CCM/DCM. In automatic

CCM/DCM mode, the controller can smoothly switch between CCM

and DCM, where converter runs at reduced switching frequency with

much higher efficiency. NCP3134 is available in 3 mm x 3 mm

QFN16 pin package.

Features

• High Efficiency in both CCM and DCM

• High Operation Frequency at 2.2 MHz

• Support MLCC Output Capacitor

• Small Footprint, 3 mm x 3 mm, 16−pin QFN Package

• Up to 4 A Continuous Output Current

• 2.9 V to 5.5 V Wide Conversion Voltage Range

• Output Voltage Range from 12% Vin to 80% Vin

• Internal 1.0 ms Soft−Start

• User Selection Between Automatic Power−Saving Mode and FCCM

Operations

• Voltage Mode Control

• Support Pre-bias Start−up Functionality

• Output Discharge Operation

• Over−Temperature Protection

• Built−in Over−Voltage, Under−Voltage and Over-Current Protection

• Power Good Indicator

• This Device is Pb−Free and is RoHS Compliant

Applications

• 5 V Step Down Rail

• 3.3 V Step Down Rail

www.onsemi.com

1

QFN16 3 x 3, 0.5P

CASE 485DA

SUGGESTED PIN ARRANGEMENT

PGND PGND VIN VIN

16 15 14 13

EN 1

12 VDD

NC 2

PGD 3

NCP3134

11 AGND

10 FB

VBST 4

9 COMP

5678

SW SW SW PS

MARKING DIAGRAM

3134

ALYWG

G

3134

A

L

Y

W

G

= Specific Device Code

= Assembly Location

= Wafer Lot

= Year

= Work Week

= Pb−Free Package

(Note: Microdot may be in either location)

ORDERING INFORMATION

See detailed ordering, marking and shipping information in the

package dimensions section on page 12 of this data sheet.

© Semiconductor Components Industries, LLC, 2016

August, 2016 − Rev. 1

1

Publication Order Number:

NCP3134/D

1 page

NCP3134

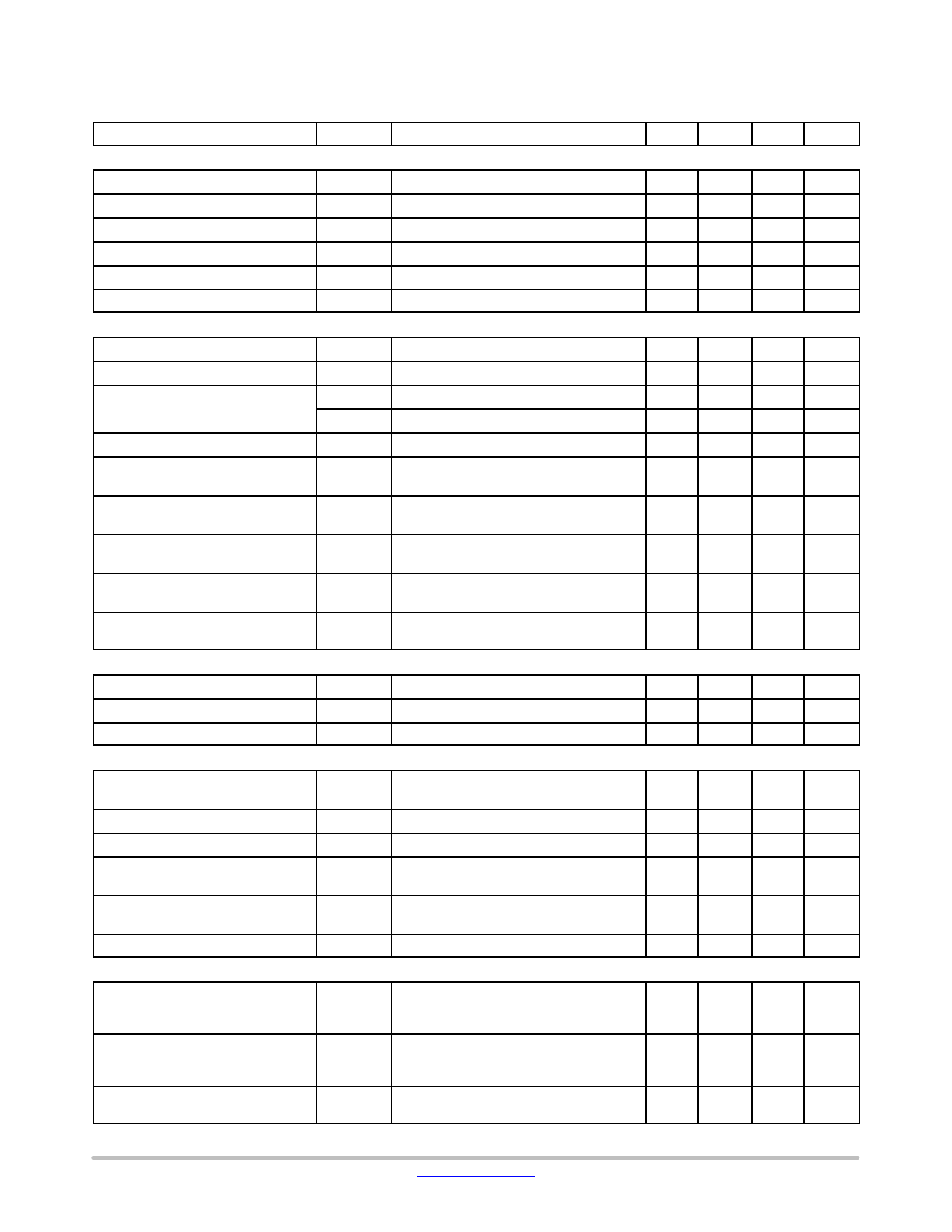

Table 4. ELECTRICAL CHARACTERISTICS (VDD = VIN = 3.3 V and VDD = VIN = 5.0 V, over recommended free air temperature

range, −40°C ≤ TJ ≤ 125°C, PGND = GND unless otherwise noted)

Parameter

Symbol

Test Conditions

Min Typ Max Units

POWER SUPPLY

VIN operation voltage

VIN Nominal input voltage range

2.9 5.5 V

VIN UVLO threshold

Ramp up; EN = ‘HI’

2.8 V

VIN UVLO hysteresis

130 mV

VDD internal bias voltage

Nominal input voltage range

2.9 5.5 V

VDD UVLO threshold

Ramp up; EN = ‘HI’

2.8 V

VDD UVLO hysteresis

75 mV

VOLTAGE MONITOR

Power good low voltage

Pull−down voltage with 4 mA sink current

200 400

mV

Power good high leakage current

−2.0 0 2.0 mA

Power good threshold

Feedback lower voltage limit

80 83 86 %Vref

Feedback higher voltage limit

114 117 120 %Vref

Power good high delay

Minimum Vin voltage for valid PGD

at start up

tPGDELAY

Measured at Vin with 1 mA (or 2 mA) sink

current on PGD pin at start up

200

1

ms

V

Output over-voltage protection

threshold at FB

114 117 120 %Vref

Over-voltage blanking time

TOVPDLY

Time from FB higher than 20% of Vref to

OVP fault

1.0 1.7 2.5

ms

Output under-voltage protection

threshold at FB

80 83 86 %Vref

Under-voltage blanking time

TUVPDLY

Time from FB lower than 20% of Vref to

UVP fault

6.5 ms

SUPPLY CURRENT (TJ = +255C)

VDD quiescent current

IVDD EN = ‘HI’, no switching

2.0 3.5 mA

VDD shutdown supply current

IVDD_SD

Vin shutdown supply current

IQSHDN

FEEDBACK VOLTAGE & ERROR AMPLIFIER

EN = ‘LO’, VDD = 3.3 V and 5.5 V

EN = ‘LO’, VDD = 3.3 V and 5.5 V

9.0 mA

4.0 mA

Reference voltage at FB

Unity gain bandwidth (Note 1)

VREF

0°C < TA < 85°C

−40°C < TA < 105°C

594

592.5

600 606

600 607.5

mV

14 MHz

Open loop gain (Note 1)

80 dB

FB pin leakage current (Note 2)

Output sourcing and sinking current

(Note 1)

−40°C < TA < 85°C

−40°C < TA < 125°C

Ccomp = 20 pF

100 nA

200 nA

5 mA

Slew rate (Note 1)

5 V/ ms

OVER CURRENT PROTECTION & ZERO CROSSING

Over-current limit on high−side FET

One time over-current latch off on

the low−side FET

Zero crossing comparator internal

offset (Note 1)

When Iout exceeds this threshold for 4

consecutive cycles. Vin = 3.3 V, Vout =

1.5 V with 1 mH inductor, TA = +25°C

4.6 5.2 5.8

Immediately shut down when sensed cur-

rent reach this value. Vin = 3.3 V, Vout =

1.5 V with 1 mH inductor, TA = +25°C

6.8

7.8

PGND−SWN, Automatic CCM/DCM mode −4.5 −3.0 −1.5

A

A

mV

www.onsemi.com

5

5 Page

NCP3134

PROTECTIONS

Under Voltage Lockout (UVLO)

There is under-voltage lock out protection (UVLO) for

both VIN and VDD in NCP3134, which has a typical trip

threshold voltage 2.8 V and trip hysteresis 75 mV for VDD

and 130 mV for VIN. If UVLO is triggered, the device resets

and waits for the voltage to rise up over the threshold voltage

and restart the part. Please note this protection function

DOES NOT trigger the fault counter to latch off the part.

Over Voltage Protection (OVP)

When feedback voltage is above 17% (typical) of nominal

voltage for over 1.7 ms blanking time, an OV fault is set. In

this case, the converter de−asserts the PGD signal and

performs the over−voltage protection function. The top gate

drive is turned off and the bottom gate drive is turned on to

discharge the output. The bottom gate drive will be turned

off until VFB drops below the UVP threshold. The device

enters a high−impedance state. This protection is latched.

Under Voltage Protection (UVP)

Output under−voltage protection works in conjunction

with the current protection described in the Over−current

Protection sections. An UVP circuit monitors the feedback

voltage to detect under−voltage event. The under−voltage

limit is 17% (typical) below of nominal voltage at FB pin.

If the feedback voltage is below this threshold over 6.5 ms,

an UV fault is set and both the high−side and the low−side

FETs turn off. This protection is latched.

Power Good Monitor (PGD)

NCP3134 provides window comparator to monitor the

output voltage at FB pin. When the output voltage is within

±17% of regulation voltage, the power good pin outputs a

high signal. Otherwise, PGD stays low. The PGD pin is open

drain 5 mA pull down output. During startup, PGD stays low

until the feedback voltage is within the specified range for

about 0.2 ms. If feedback voltage falls outside the tolerance

band, the PG pin goes low after 10 ms delay.

The PGD pin de−asserts as soon as the EN pin is pulled

low or an under−voltage event on VDD is detected.

Over Current Protection (OCP)

NCP3134 provides both high−side and low−side

MOSFET current limiting. When the current through the

high−side FET exceeds 5.2 A, the high−side FET turns off

and the low−side FET turns on until next PWM cycle. An

over−current counter is triggered and starts to increment

each occurrence of an over−current event. Both the

high−side and the low−side FETs turn off when the OC

counter reaches four. The OC counter resets if the detected

current is less than 5.2 A after an OC event.

Another set of over−current circuitry monitors the current

flowing through the low−side FET. If the current through the

low−side FET exceeds 7.8 A, the over−current protection is

enabled and immediately turns off both the high−side and

the low−side FETs. The device is fully protected against

over−current during both on−time and off−time. This

protection is latched.

Pre−Bias Startup

In some applications the controller will be required to start

switching when its output capacitors are charged anywhere

from slightly above 0 V to just below the regulation voltage.

This situation occurs for a number of reasons: the

converter’s output capacitors may have residual charge on

them or the converter’s output may be held up by a low

current standby power supply. NCP3134 supports pre−bias

start up by holding low−side FETs off until soft start ramp

reaches the FB pin voltage.

Thermal Shutdown

The NCP3134 protects itself from over heating with an

internal thermal monitoring circuit. When the die

temperature goes beyond a threshold value 160°C, both the

high−side and the low−side FETs turn off until the

temperature falls 10°C below of the threshold value. Then

the converter restarts.

Application Note

For higher output voltage application cases (Vout =

3.3 V), choose the inductor value not to be lower than 1 mH

to avoid over-current protection being triggered by inductor

current ripple. For VIN=5V and VOUT=3.3V case, add a

voltage divider between VIN and EN to ensure that the part

can start up without triggering UVP. Use the following

figure as design reference for schematics. For other lower

output voltage cases, it is not necessary to add this divider.

VIN = 5 V

10 kW

EN

3.6 kW

PGND

Output current at the transition between CCM and DCM

can be calculated in the following equation:

Io = 0.5 x (Vin−Vo) x Vo/Vin/fs/L

Io − output current at boundary of CCM and DCM;

Vin − input voltage;

Vo − output voltage;

fs − switching frequency;

L − inductor

www.onsemi.com

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet NCP3134.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NCP3133A | 3A Integrated Synchronous Buck Converter | ON Semiconductor |

| NCP3134 | 4A Integrated Synchronous Buck Converter | ON Semiconductor |

| NCP3135 | 5A Integrated Synchronous Buck Converter | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |