|

|

PDF UT54ACS109E Data sheet ( Hoja de datos )

| Número de pieza | UT54ACS109E | |

| Descripción | Dual J-K Flip-Flops | |

| Fabricantes | Aeroflex Circuit Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UT54ACS109E (archivo pdf) en la parte inferior de esta página. Total 10 Páginas | ||

|

No Preview Available !

UT54ACS109E

Dual J-K Flip-Flops

Septenber 2010

www.aeroflex.com/Logic

FEATURES

• 0.6μm CRH CMOS Process

- Latchup immune

• High speed

• Low power consumption

• Wide operating power supply of 3.0V to 5.5V

• Available QML Q or V processes

• 16-lead flatpack

DESCRIPTION

The UT54ACS109E is a dual J-K positive triggered flip-flop.

A low level at the preset or clear inputs sets or resets the outputs

regardless of the other input levels. When preset and clear are

inactive (high), data at the J and K input meeting the setup time

requirements are transferred to the outputs on the positive-going

edge of the clock pulse. Following the hold time interval, data

at the J and K input can be changed without affecting the levels

at the outputs. The flip-flops can perform as toggle flip-flops

by grounding K and tying J high. They also can perform as D

flip-flops if J and K are tied together.

The devices are characterized over full HiRel temperature range

of -55°C to +125°C.

FUNCTION TABLE

PRE

L

H

L

H

H

H

H

H

INPUTS

CLR

CLK

HX

LX

LX

H↑

H↑

H↑

H↑

HL

OUTPUT

JK Q

Q

XX H

L

XX L

H

X X H1 H1

LL

L

H

HL

Toggle

L H No Change

HH H

L

X X No Change

Note:

1. The output levels in this configuration are not guaranteed to meet the mini-

mum levels for VOH if the lows at preset and clear are near VIL maximum.

In addition, this configuration is nonstable; that is, it will not persist when

either preset or clear returns to its inactive (high) level.

PINOUTS

CLR1

J1

K1

CLK1

PRE1

Q1

Q1

VSS

16-Lead Flatpack

Top View

1 16

2 15

3 14

4 13

5 12

6 11

7 10

89

VDD

CLR2

J2

K2

CLK2

PRE2

Q2

Q2

LOGIC SYMBOL

PRE1

J1

CLK1

K1

CLR1

(5)

(2)

(4)

(3)

(1)

S

J1

C1

K1

R

(6) Q1

(7)

Q1

(11)

PRE2

(14)

J2

(12)

CLK2

(13)

K2

(15)

CLR2

(10)

Q2

(9) Q2

Note:

1. Logic symbol in accordance with ANSI/IEEE standard 91-1984 and

IEC Publication 617-12.

1

1 page

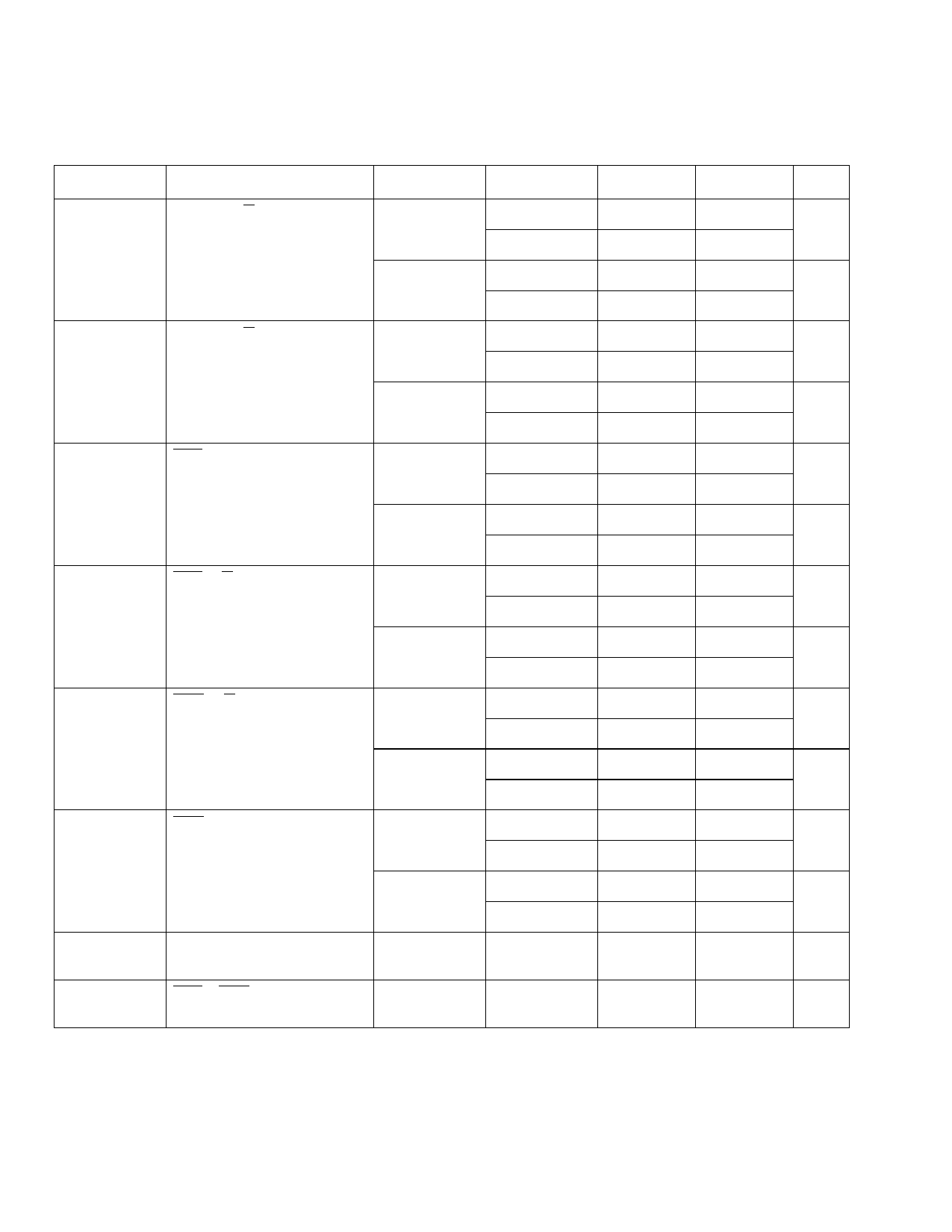

AC ELECTRICAL CHARACTERISTICS FOR THE UT54ACS109E2

(VDD = 3.0V to 5.5V; VSS = 0V 1, -55°C < TC < +125°C)

SYMBOL

PARAMETER

VDD

tPLH1

CLK to Q, Q

CL = 30pF

3.0V & 3.6V

4.5V & 5.5V

CL = 50pF

3.0V & 3.6V

4.5V & 5.5V

tPHL1

CLK to Q, Q

CL = 30pF

3.0V & 3.6V

4.5V & 5.5V

CL = 50pF

3.0V & 3.6V

4.5V & 5.5V

tPLH2

PRE to Q

CL = 30pF

3.0V & 3.6V

4.5V & 5.5V

CL = 50pF

3.0V & 3.6V

4.5V & 5.5V

tPHL2

PRE to Q

CL = 30pF

3.0V & 3.6V

4.5V & 5.5V

CL = 50pF

3.0V & 3.6V

4.5V & 5.5V

tPLH3

CLR to Q

CL = 30pF

3.0V & 3.6V

4.5V & 5.5V

CL = 50pF

3.0V & 3.6V

4.5V & 5.5V

tPHL3

CLR to Q

CL = 30pF

3.0V & 3.6V

4.5V & 5.5V

CL = 50pF

3.0V & 3.6V

4.5V & 5.5V

fMAX4

Maximum clock frequency

CL = 50pF 3.0V, 4.5V, and

5.5V

tSU1 PRE or CLR inactive setup time CL = 50pF 3.0V, 4.5V, and

before CLK↑

5.5V

MINIMUM MAXIMUM UNIT

4 23 ns

4 19

4 27 ns

4 23

5 27 ns

5 23

5 31 ns

5 27

1 16 ns

1 12

1 20 ns

1 16

1 19 ns

1 15

1 23 ns

1 19

2 16 ns

2 12

2 20 ns

2 16

2 19 ns

2 15

2 23 ns

2 19

62 MHz

5 ns

5

5 Page | ||

| Páginas | Total 10 Páginas | |

| PDF Descargar | [ Datasheet UT54ACS109E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UT54ACS109 | Radiation-Hardened Dual J-K Flip-Flops | Aeroflex Circuit Technology |

| UT54ACS109E | Dual J-K Flip-Flops | Aeroflex Circuit Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |