|

|

PDF SMB113B Data sheet ( Hoja de datos )

| Número de pieza | SMB113B | |

| Descripción | Four-channel Programmable DC-DC System Power Managers | |

| Fabricantes | Summit | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SMB113B (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

SMB113A/B/SMB117/A

Preliminary Information

High-power, Four-channel Programmable DC-DC System Power Managers

FEATURES & APPLICATIONS

• Digital programming of all major parameters via

I2C interface and non-volatile memory

• Output voltage set point

• Input/battery voltage monitoring

• Output power-up/down sequencing

• Digital soft-start and output slew rate

• Dynamic voltage control of all outputs

• UV/OV monitoring of all outputs

• Enable/Disable outputs independently

• User friendly Graphical User Interface (GUI)

• Four synchronous step-down output channels

• Integrated RESET monitor

• +2.7V to +6.0V Input Range

• Highly accurate output voltage: <1.5%

• Factory programmable dead times

• 0% to 100% Duty Cycle operation

• Undervoltage Lockout (UVLO) with hysteresis

• 250kHz (SMB117A), 400kHz (SMB117), 800kHz

(SMB113A), 1MHz (SMB113B) operating frequency

• 96 bytes of user configurable nonvolatile memory

Applications

• Car & Marine Navigation Systems

• Set-top Boxes

• TVs

• DDR Memory

• Mobile Computing/PDAs

• Office Equipment

• DMB Systems

SIMPLIFIED APPLICATIONS DRAWING

INTRODUCTION

The SMB113A/B and SMB117/A are highly integrated and

flexible four-channel power managers designed for use in a

wide range of applications. The built-in digital programmability

allows system designers to custom tailor the device to suit

almost any multi-channel power supply application from digital

camcorders to set-top boxes. Complete with a user friendly

GUI, all programmable settings, including output voltages and

input/output voltage monitoring, can be customized with ease.

The SMB113A/B and SMB117/A integrate all the essential

blocks required to implement a complete four-channel power

subsystem consisting of four synchronous step-down “buck”

controllers. Additionally sophisticated power control/monitoring

functions required by complex systems are built-in. These

include digitally programmable output voltage set point, power-

up/down sequencing, enable/disable, dynamic voltage

management and UV/OV monitoring on all channels.

The integration of features and built-in flexibility of the

SMB113A/B and SMB117/A allows the system designer to

create a “platform solution” that can be easily modified via

software without major hardware changes. Combined with the

re-programmability of the SMB113A/B and SMB117/A, this

facilitates rapid design cycles and proliferation from a base

design to future product generations.

The SMB113A/B and SMB117/A are suited to a wide variety of

applications with an input range of +2.7V to +6.0V. Higher

input voltage operation can easily be implemented with a small

number of external components. Output voltages are

extremely accurate (<1.5%). Communication is accomplished

via the industry standard I2C bus. All user-programmed

settings are stored in non-volatile EEPROM of which 96 bytes

may be used as general-purpose memory. The devices are

offered in both the commercial and the industrial operating

temperature range. The package type is a lead-free, RoHS

compliant, 5x5 QFN-32.

+2.7V to +6.0V

or

Li-Ion

I2C/SMBus

Enable Input

Reset Input

RESET Output

(Power Good)

SMB113A/B

System

Control

and

Monitoring

4 Step-

Down

(Buck)

Channels

RESET

Monitor

+0.5V to Vin (Prog.) @ 1.5A/5A

CPU Core

+0.5V to Vin (Prog.) @ 1.5A/5A Memory, I/O

+0.5V to Vin (Prog.) @ 1.5A/5A

DSP/Codec

+0.5V to Vin (Prog.) @ 1.5A/5A

Analog/RF

+2.7V to +6.0V

or

Li-Ion

I2C/SMBus

Enable Input

Reset Input

RESET Output

(Power Good)

SMB117/A

System

Control

and

Monitoring

4 Step-

Down

(Buck)

Channels

RESET

Monitor

+0.5V to Vin (Prog.) @ 5A/10A

CPU Core

+0.5V to Vin (Prog.) @ 5A/10A

Memory, I/O

+0.5V to Vin (Prog.) @ 5A/10A

DSP/Codec

+0.5V to Vin (Prog.) @ 5A/10A

Analog/RF

Figure 1 – Applications schematic featuring the SMB113A/B/117/A programmable DC-DC controllers.

Note: This is an applications example only. Some pins, components and values are not shown.

© SUMMIT Microelectronics, Inc. 2007

757 N. Mary Avenue • Sunnyvale CA 94085

http://www.summitmicro.com/

2111 2.5 6/11/2010

Phone 408 523-1000 • FAX 408 523-1266

1

1 page

PIN DESCRIPTION

Pin Number Pin Type

1 OUT

2 OUT

3 IN

4 IN

5 IN

6 I/O

7 IN

8 OUT

9 PWR

10 OUT

11 IN

12 IN

13 IN

Summit Microelectronics, Inc

SMB113A/B/SMB117/A

Preliminary Information

Pin Name

HSDRV_CH0

HEALTHY

(nRESET)

COMP1_CH0

COMP2_CH0

VM_CH0

SDA

SCL

LSDRV_CH1

HVSUP1

HSDRV_CH1

HOST_RESET

COMP1_CH1

COMP2_CH1

Pin Description

The HSDRV_CH0 (Channel 0 High-side Driver) pin is the upper

switching node of the channel 0 synchronous step-down buck

controller. Attach to the gate of p-channel MOSFET. A delay

exists between the assertion of HSDRV_CH0 and assertion of

LSDRV_CH0 to prevent excessive current flow during switching.

The HEALTHY pin is an open drain output. High when all

enabled output supplies are within the programmed levels.

HEALTHY will ignore any disabled supply. There is a

programmable glitch filter on the under-voltage and over-voltage

sensors so that short transients outside of the limits will be

ignored by HEALTHY. This pin can also be programmed to act

as a Reset Output (nRESET). In this case, it releases with a

programmable delay after all outputs are valid. When used, this

pin should be pulled high by an external pull-up resistor.

The COMP1_CH0 (Channel 0 primary Compensation) pin is the

primary feedback input of the channel 0 step-down buck

controller. The COMP1_CH0 pin is internally connected to a

programmable resistor divider.

The COMP2_CH0 (Channel 0 secondary Compensation) pin is

the secondary feedback input of the channel 0 step-down buck

controller.

The VM_CH0 (Channel 0 Voltage Monitor) pin connects the

channel 0 step-down controller output. Internally the VM_CH0 pin

connects to a programmable resistor divider.

SDA (Serial Data) is an open drain bi-directional pin used as the

I2C data line. SDA must be tied high through a pull-up resistor.

SCL (Serial Clock) is an open drain input pin used as the I2C

clock line. SCL must be tied high through a pull-up resistor.

The LSDRV_CH1 (Channel 1 Low-side Driver) pin is the lower

switching node of the channel 1 synchronous step-down buck

controller. Attach to the gate of n-channel MOSFET.

Channel 1 High Voltage Supply for Channel 1 buck driver.

The HSDRV_CH1 (Channel 1 High-side Driver) pin is the upper

switching node of the channel 1 synchronous step-down buck

controller. Attach to the gate of p-channel MOSFET. A delay

exists between the assertion of HSDRV_CH1 and assertion of

LSDRV_CH1 to prevent excessive current flow during switching.

The HOST_RESET pin is an active high reset input. When this

pin is asserted high, the nRESET output will immediately go low.

When HOST_RESET is brought low, nRESET will go high after a

programmed reset delay. When pin 2 is used as a HEALTHY

output, this pin needs to be attached to GND or VBATT via a

resistor.

The COMP1_CH1 (Channel 1 primary Compensation) pin is the

primary compensation input of the channel 1 step-down buck

controller. The COMP1_CH1 pin is internally connected to a

programmable resistor divider.

The COMP2_CH1 (Channel 1 secondary Compensation) pin is

the secondary compensation input of the channel 1 step-down

buck controller.

2111 2.5 6/11/2010

5

5 Page

SMB113A/B/SMB117/A

Preliminary Information

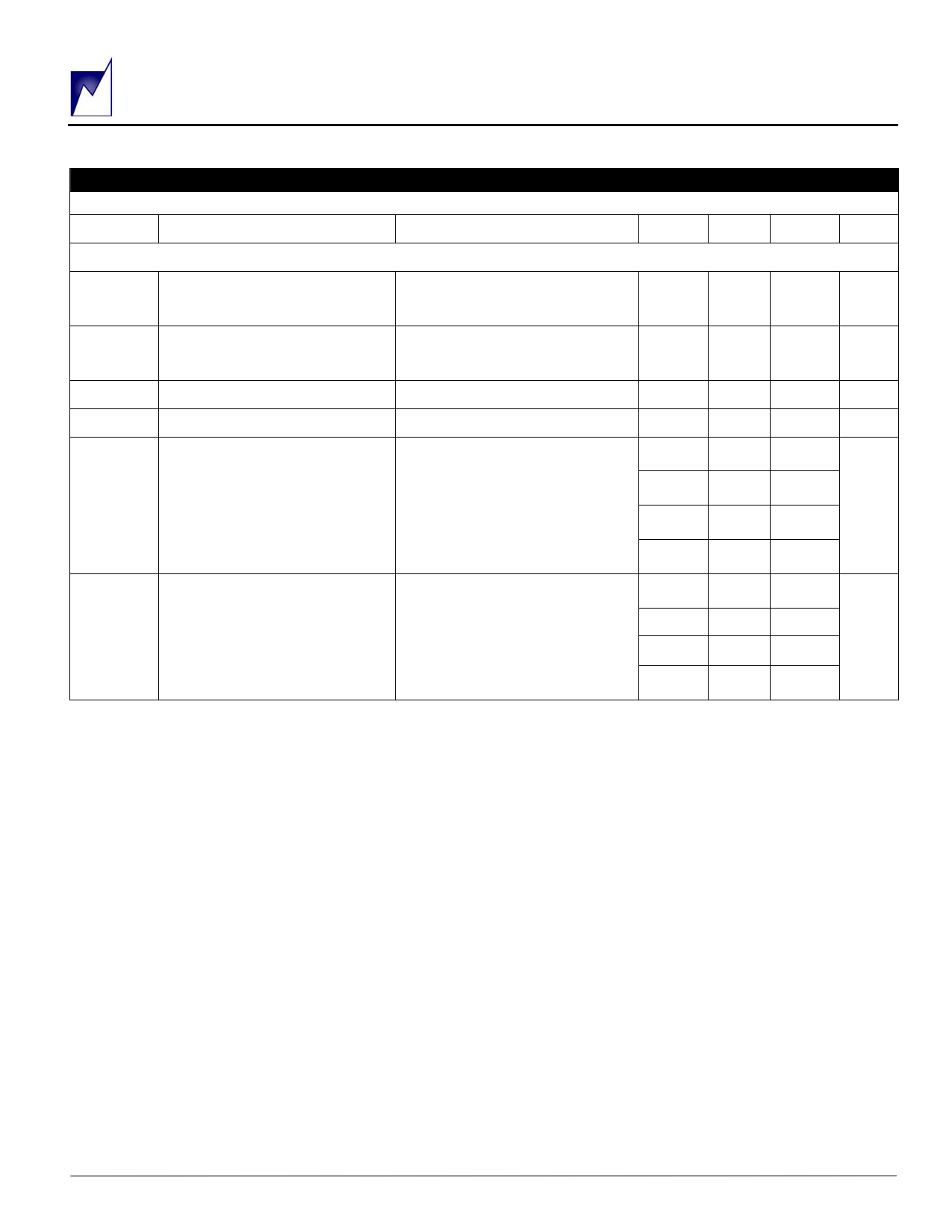

DC OPERATING CHARACTERISTICS (CONTINUED)

(Over recommended operating conditions, unless otherwise noted. All voltages are relative to GND.)

Symbol Parameter

Conditions

Min Typ Max

Programmable Monitoring Thresholds

VPUV1

VPUV2

Programmable UV1 threshold

Programmable UV2 threshold

Programmable UV1 threshold

voltage measured on VBATT pin

in 150 mV increments

Programmable UV2 threshold

voltage measured on VBATT pin

in 150 mV increments

2.55

2.55

3.60

3.60

∆VPUV2

UV2 accuracy

±2

∆VPUV1

UV1 accuracy

±2

-3 -5 -7

PUVTH

Programmable under-voltage

threshold

Output voltage relative to

nominal operating voltage.

Note 3.

-8 -10 -12

-12 -15 -18

-16 -20 -24

POVTH

Programmable over-voltage

threshold

Output voltage relative to

nominal operating voltage.

Note 3.

+3 +5 +7

+8 +10 +12

+12 +15 +18

+16 +20 +24

Unit

V

V

%

%

%

%

Note 1: Voltage accuracies are only guaranteed for factory-programmed settings. Changing the output voltage from that reflected in the customer

specific CSIR code might result in inaccuracies exceeding those specified above by 1%.

Note 2: For more accurate active current levels under several load conditions, Summit’s proprietary design software can be used. Contact the

factory for more information.

Note 3: Guaranteed by Design and Characterization – not 100% tested in Production.

Note 4: Contact the factory for designs that require an input voltage lower than 4.5V.

Summit Microelectronics, Inc

2111 2.5 6/11/2010

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet SMB113B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SMB113 | Four Channel Programmable DC-DC System Power Manager | Summit |

| SMB113A | Four-channel Programmable DC-DC System Power Managers | Summit |

| SMB113B | Four-channel Programmable DC-DC System Power Managers | Summit |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |